MICROCOMPUTER

MN101C

MN101C78A/F78A LSI User's Manual

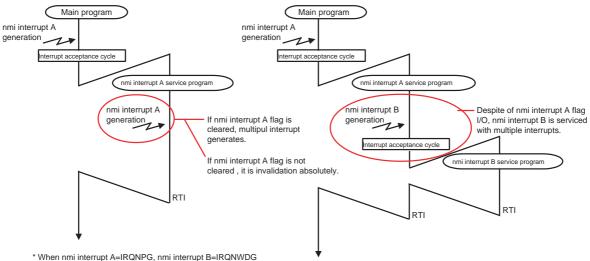

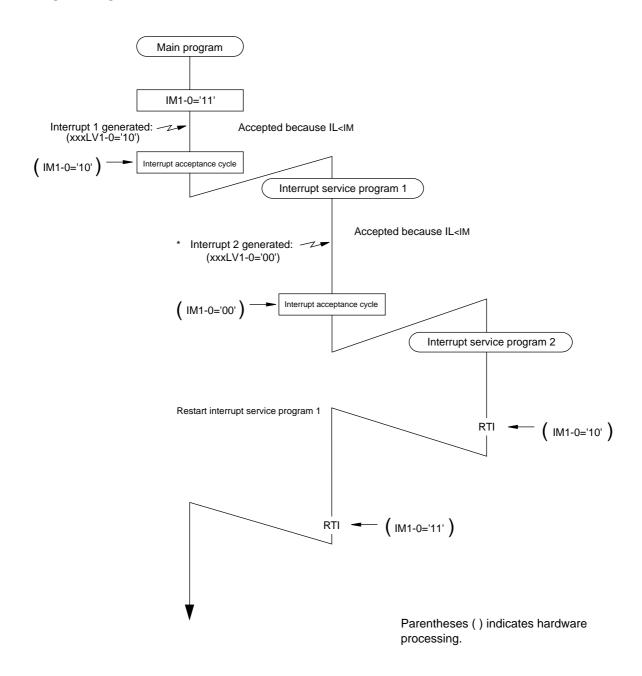

Pub.No.21478-013E

PanaXSeries is a trademark of Matsushita Electric Industrial Co., Ltd.

The other corporation names, logotype and product names written in this book are trademarks or registered trademarks of their corresponding corporations.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this book is limited to showing representative characteristics and applied circuits examples of the products. It neither warrants non-infringement of intellectual property right or any other rights owned by our company or a third party, nor grants any license.

- (3) We are not liable for the infringement of rights owned by a third party arising out of the use of the product or technologies as described in this book.

- (4) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (5) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (6) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage, and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (7) When using products for which damp-proof packing is required, observe the conditions (including shelf life and amount of time let standing of unsealed items) agreed upon when specification sheets are individually exchanged.

- (8) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.

If you have any inquiries or questions about this book or our semiconductors, please contact one of our sales offices listed at the back of this book.

## About This Manual

### ■Organization

In this LSI manual, this LSI functions are presented in the following order: overview, basic CPU functions, interrupt functions, port functions, timer functions, serial functions, and other peripheral hardware functions. Each section contains overview of function, block diagram, control register, operation, and setting example.

### ■Manual Configuration

Each section of this manual consists of a title, summary, main text, key information, precautions and warnings, and references. The layout and definition of each section are shown below.

### ■Finding Desired Information

This manual provides three methods for finding desired information quickly and easily.

- 1. Consult the index at the front of the manual to locate the beginning of each section.

- 2. Consult the table of contents at the front of the manual to locate desired titles.

- 3.A chapter number and its chapter title are located at the top corner of each page, and section titles are located at the bottom corner of each page.

#### ■Related Manuals

Note that the following related documents are available.

- "MN101C Series LSI user's Manual"

Describes the device hardware>

- "MN101C Series Instruction Manual"

- <Describes the instruction set.>

- " Series C Compiler User's Manual: Usage Guide" <Describes the installation, the commands, and options of the C Compiler.>

- "MN101C Series C Compiler User's Manual: Language Description" < Describes the syntax of the C Compiler.>

- "MN101C Series C Compiler User's Manual: Library Reference" < Describes the standard library of the C Compiler.>

- "MN101C Series Cross-assembler User's Manual" < Describes the assembler syntax and notation.>

- "MN101C Series C Source Code Debugger User's Manual" <Describes the use of C source code debugger.>

- About This Manual "MN101C Series PanaX Series Installation Manual"

Describes the installation of C compiler, cross-assembler and C source code debugger and the procedure for bringing up the in-circuit emulator.>

### Contents

Chapter 1 Overview

Chapter 2 CPU Basics

Chapter 3 Interrupts

Chapter 4 I/O Ports

Chapter 5 8-Bit Timers

Chapter 6 16-Bit Timers

Chapter 7 Time Base Timer/Free-running Timer

Chapter 8 Remote Control Career

Chapter 9 Watchdog Timer

Chapter 10 Buzzer

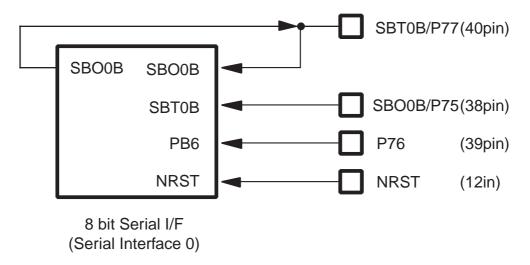

Chapter 11 Serial Interface 0

Chapter 12 Serial Interface 1

0

1

2

3

4

5

6

7

8

9

10

11

12

Chapter 13 Serial Interface 3

Chapter 14 Serial Interface 4

Chapter 15 A/D Converter

Chapter 16 LCD

Chapter 17 Appendix

13

14

15

16

17

Contents

# 0

### Contents

| Chapter 1 Overview                                                    | I-1   |

|-----------------------------------------------------------------------|-------|

| 1.1 Overview                                                          | I-2   |

| 1.1.1 Overview                                                        |       |

| 1.1.2 Product Summary                                                 |       |

| 1.2 Hardware Functions                                                | I-3   |

| 1.3 Pin Description                                                   | I-10  |

| 1.3.1 Pin configuration                                               |       |

| 1.3.2 Pin Specification                                               |       |

| 1.3.3 Pin Functions                                                   |       |

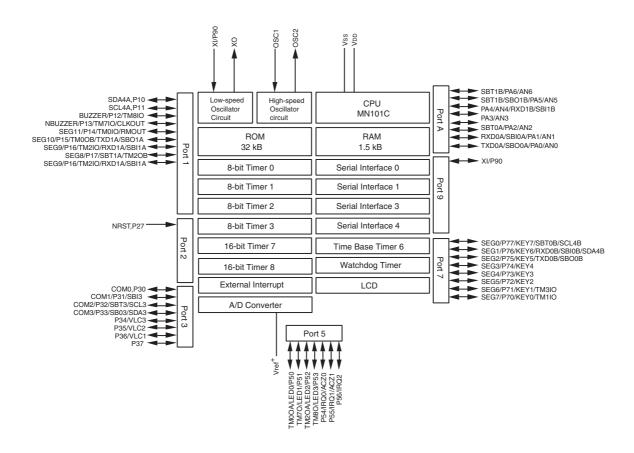

| 1.4 Block Diagram                                                     | I-20  |

| 1.4.1 Block Diagram                                                   |       |

| 1.5 Electrical Characteristics                                        | I-21  |

| 1.5.1 Absolute Maximum Ratings *2,*3                                  |       |

| 1.5.2 Operating Conditions [NORMAL mode:fs=fosc/2, SLOW mode:fs=fx/2] |       |

| 1.5.3 DC Characteristics                                              |       |

| 1.5.4 A/C Converter Characteristics                                   |       |

| 1.5.5 A/D Converter Characteristics                                   |       |

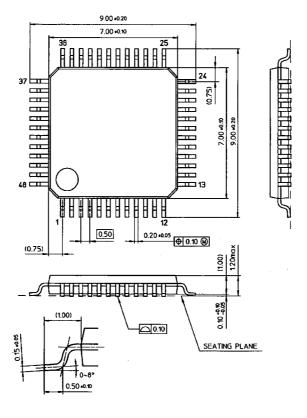

| 1.6 Package Dimension                                                 | I-34  |

| 1.7 Cautions for Circuit Setup                                        | I-35  |

| 1.7.1 General Usage                                                   |       |

| 1.7.2 Unused pins                                                     |       |

| 1.7.3 Power Supply                                                    |       |

| 1.7.4 Power Supply Circuit                                            |       |

| Chapter 2 CPU Basics                                                  | II-1  |

| 2.1 Overview                                                          | II-2  |

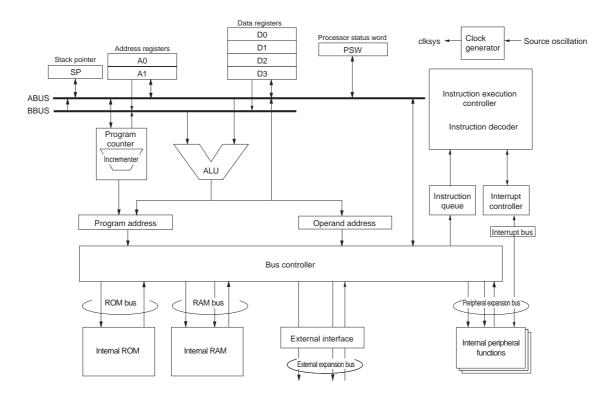

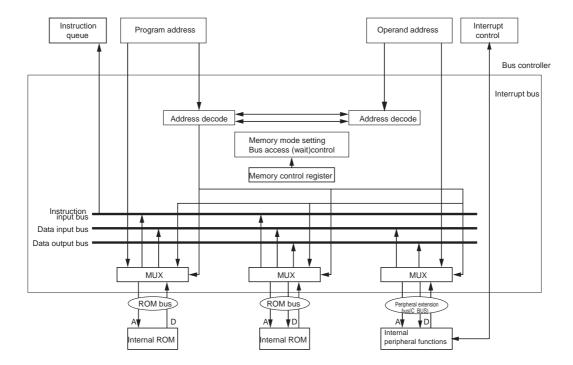

| 2.1.1 Block Diagram                                                   | II-4  |

| 2.1.2 CPU Control Registers                                           | II-6  |

| 2.1.3 Instruction Execution Controller                                | II-7  |

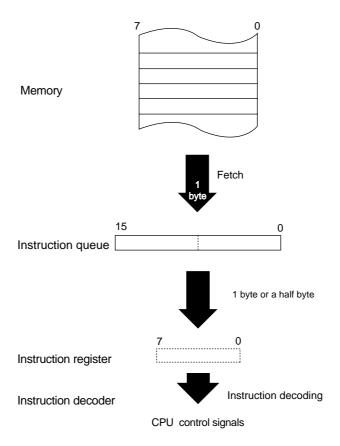

| 2.1.4 Pipeline Process                                                | II-8  |

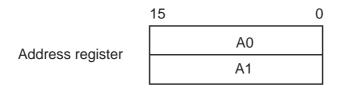

| 2.1.5 Registers for Address                                           | II-8  |

| 2.1.6 Registers for Data                                              | II-9  |

| 2.1.7 Processor Status Word                                           |       |

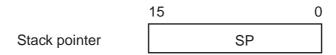

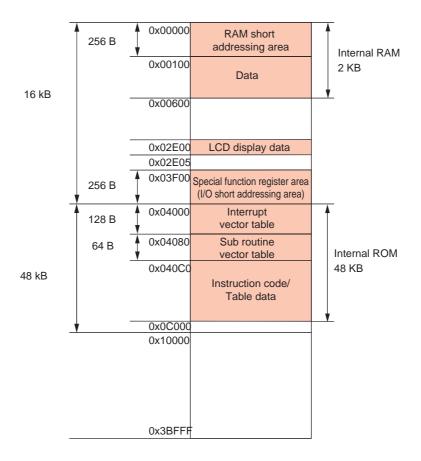

| 2.1.8 Address Space                                                   | II-12 |

| 2.1.9 Addressing Modes                                                |       |

| 2.1.10 Machine Clock                                                  |       |

| 2.2 Memory Space                                                      | II-16 |

| 2.2.1 Memory Mode                            | II-16  |

|----------------------------------------------|--------|

| 2.2.2 Single-chip Mode                       | II-17  |

| 2.2.3 Special Function Registers             | II-18  |

| 2.3 Bus Interface                            | II-19  |

| 2.3.1 Bus Controller                         | II-19  |

| 2.3.2 Control Registers                      | II-20  |

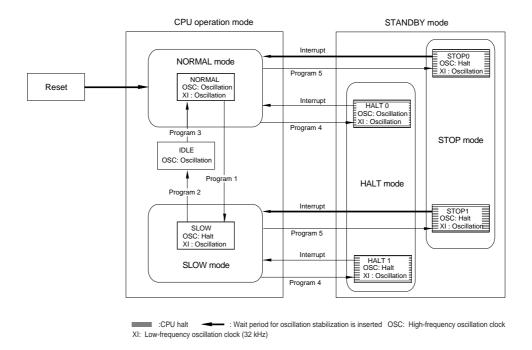

| 2.4 Standby Function                         | II-21  |

| 2.4.1 Overview                               |        |

| 2.4.2 CPU Mode Control Register              |        |

| 2.4.3 Transition between SLOW and NORMAL     |        |

| 2.4.4 Transition to STANDBY Modes            |        |

| 2.5 Clock Switching                          | II-28  |

| 2.6 Reset                                    | II-30  |

| 2.6.1 Reset operation                        | II-30  |

| 2.6.2 Oscillation Stabilization Wait time    | II-32  |

| Chapter 3 Interrupts                         | III-1  |

| 3.1 Overview                                 | III-2  |

| 3.1.1 Functions                              | III-3  |

| 3.1.2 Block Diagram                          | III-4  |

| 3.1.3 Operation                              | III-5  |

| 3.1.4 Interrupt Flag Setup                   | III-16 |

| 3.2 Control Registers                        | III-17 |

| 3.2.1 Registers List                         | III-17 |

| 3.2.2 Interrupt Control Registers            | III-19 |

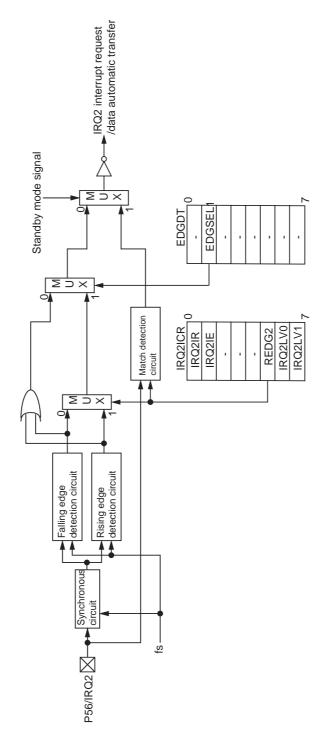

| 3.3 External Interrupts                      | III-41 |

| 3.3.1 Overview                               | III-41 |

| 3.3.2 Block Diagram                          | III-42 |

| 3.3.3 Control Registers                      | III-46 |

| 3.3.4 Programmable Active Edge Interrupt     | III-52 |

| 3.3.5 Both Edges Interrupt                   | III-53 |

| 3.3.6 Key Input Interrupt                    | III-55 |

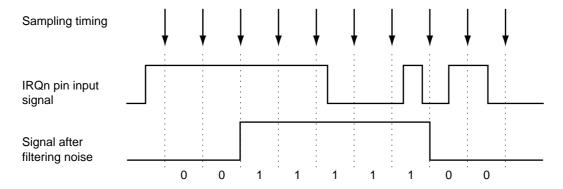

| 3.3.7 Noise Filter                           | III-56 |

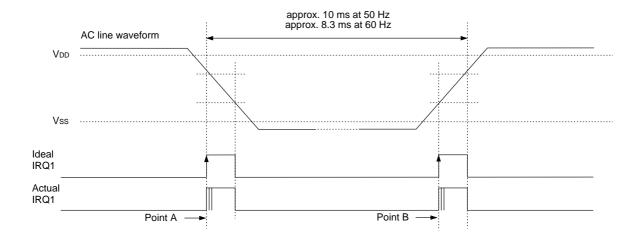

| 3.3.8 AC Zero-Cross Detector                 | III-59 |

| 3.3.9 External Interrupt At The Standby Mode | III-61 |

| Chapter 4 I/O Ports                          | IV-1   |

| 4.1 Overview                                 | IV-2   |

| 4.1.1 I/O Port Overview                      | IV-2   |

| A 1.2 I/O Port Status at Reset               | IV-2   |

| 4.1.3 Control Registers      | IV-3              |

|------------------------------|-------------------|

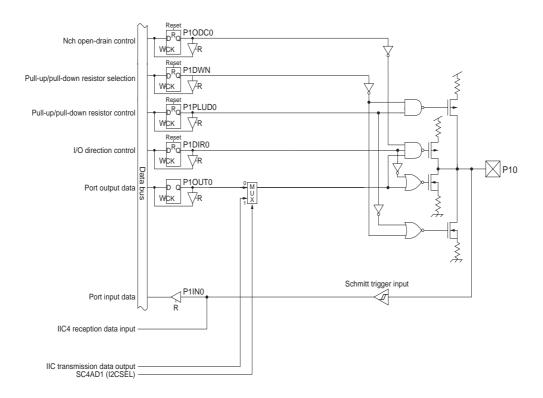

| 4.2 Port 1                   | IV-5              |

| 4.2.1 Description            | IV-5              |

| 4.2.2 Registers              |                   |

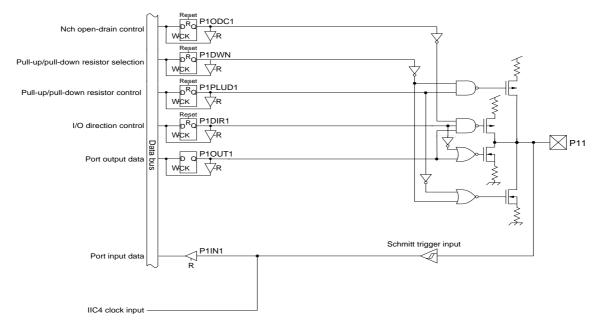

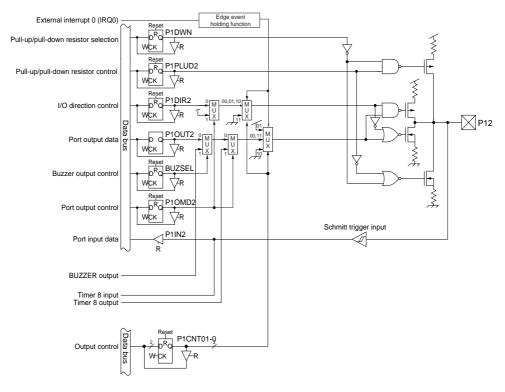

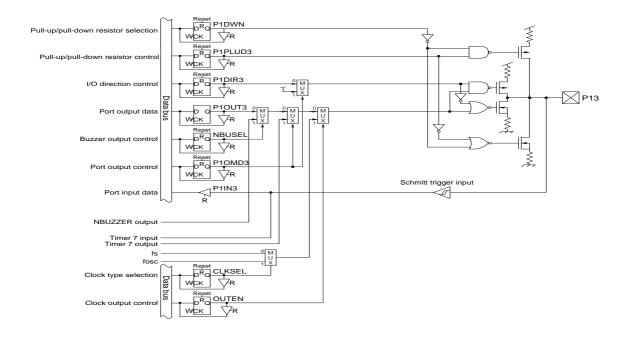

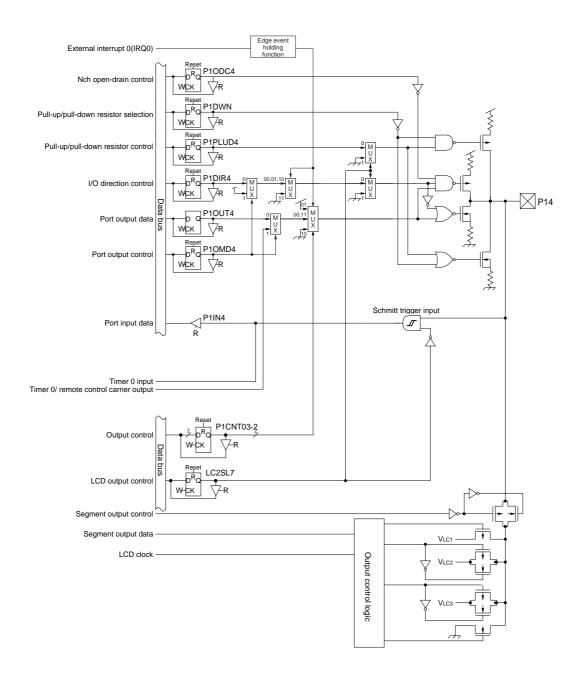

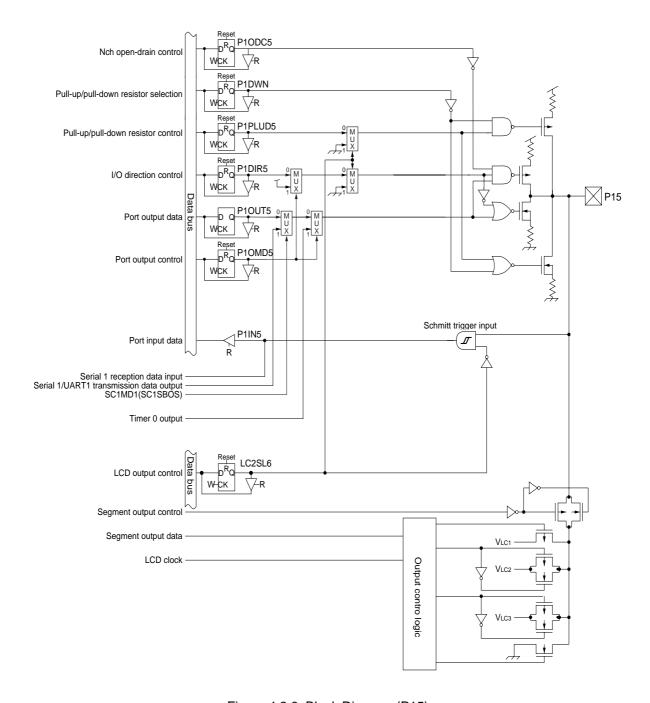

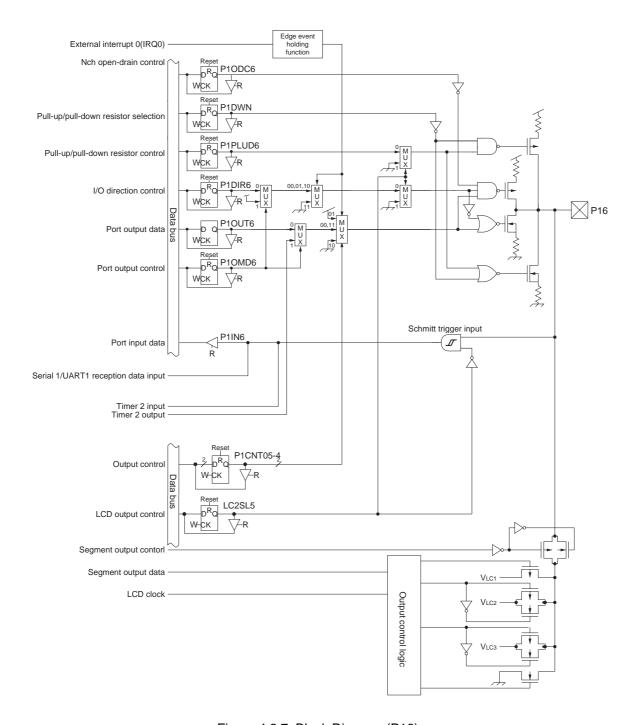

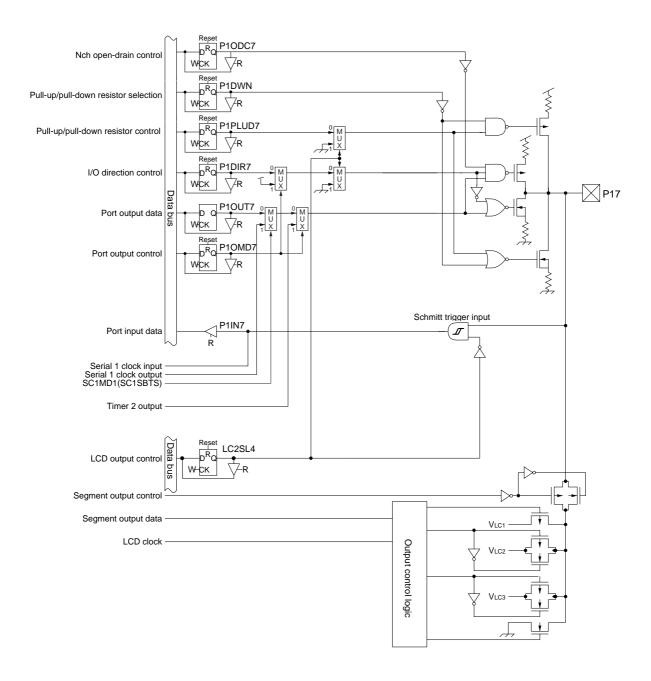

| 4.2.3 Block Diagram          |                   |

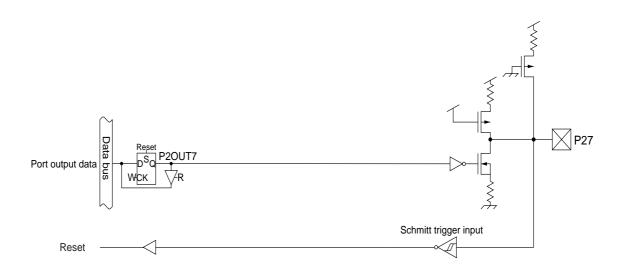

| 4.3 Port 2                   | IV-22             |

| 4.3.1 Description            | IV-22             |

| 4.3.2 Registers              | IV-22             |

| 4.3.3 Block Diagram          | IV-23             |

| 4.4 Port 3                   | IV-24             |

| 4.4.1 Description            | IV-24             |

| 4.4.2 Registers              | IV-26             |

| 4.4.3 Block Diagram          | IV-33             |

| 4.5 Port 5                   | IV-39             |

| 4.5.1 Description            | IV-39             |

| 4.5.2 Registers              | IV-41             |

| 4.5.3 Block Diagram          | IV-45             |

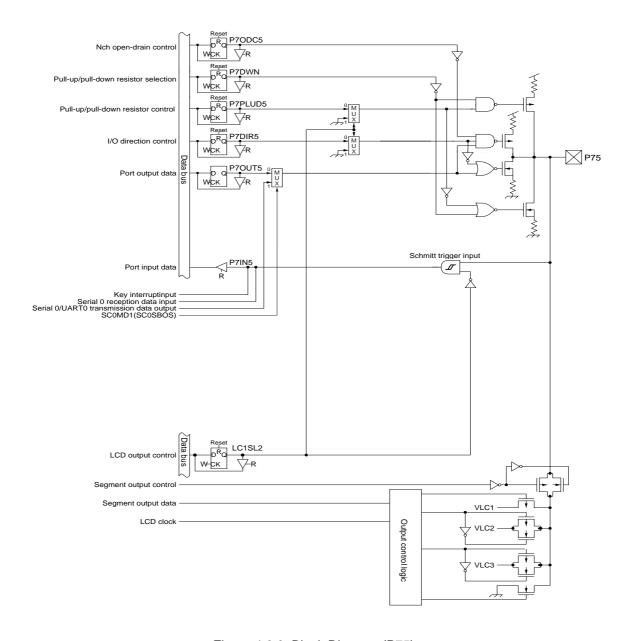

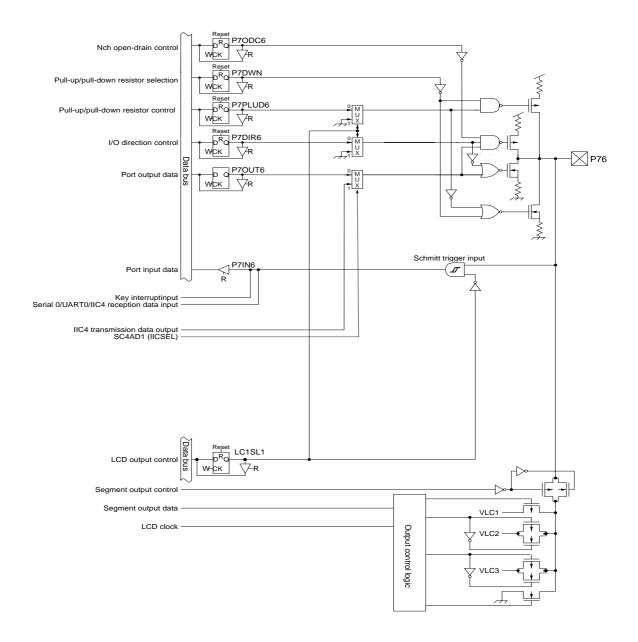

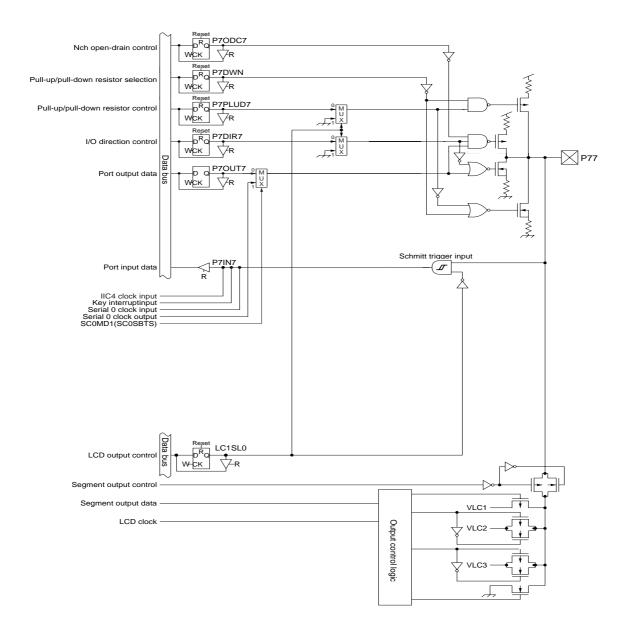

| 4.6 Port 7                   | IV-49             |

| 4.6.1 Description            | IV-49             |

| 4.6.2 Registers              | IV-51             |

| 4.6.3 Block Diagram          | IV-58             |

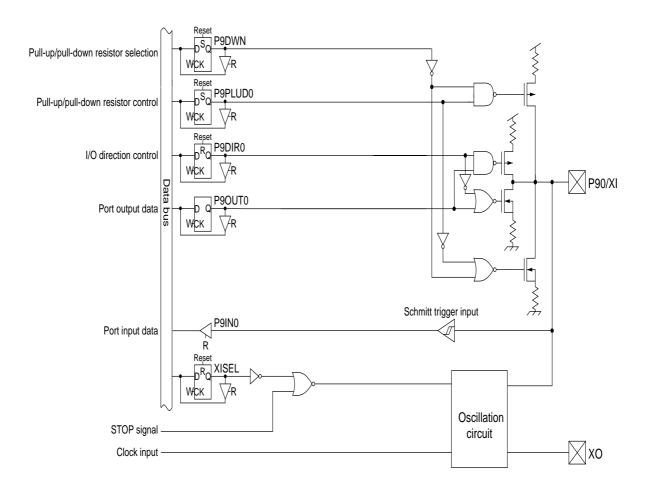

| 4.7 Port 9                   | IV-66             |

| 4.7.1 Description            | IV-66             |

| 4.7.2 Registers              | IV-67             |

| 4.7.3 Block Diagram          | IV-71             |

| 4.8 Port A                   | IV-72             |

| 4.8.1 Description            | IV-72             |

| 4.8.2 Registers              | IV-74             |

| 4.8.3 Block Diagram          | IV-78             |

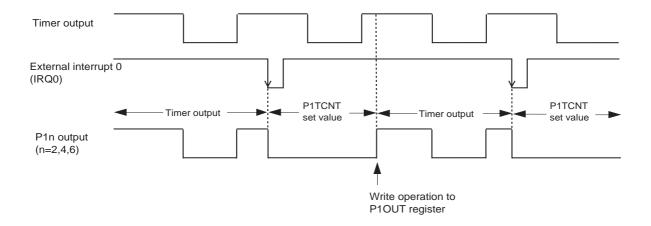

| 4.9 Real Time Output Control | IV-82             |

| 4.9.1 Registers              | IV-82             |

| 4.9.2 Operation              | IV-82             |

| apter 5 8-bit Timers         | V-1               |

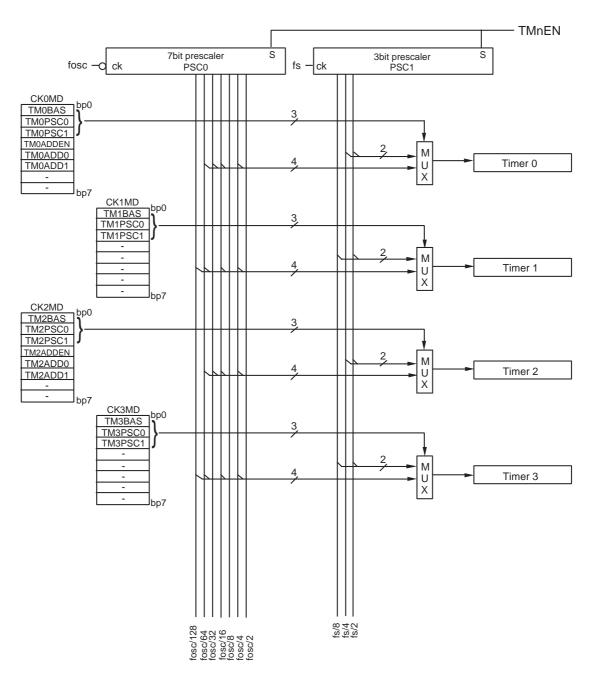

| 5.1 Overview                 | V-2               |

| 5.1.1 Functions              |                   |

| 5.1.2 Block Diagram          |                   |

| 5.2 Control Registers        | V-7               |

| 5 9 1 Pagistars              | $\mathbf{V}_{-}7$ |

| 5.2.2 Timer Prescaler Registers        | V-9   |

|----------------------------------------|-------|

| 5.2.3 Programmable Timer Registers     | V-12  |

| 5.2.4 Timer Mode Registers             | V-14  |

| 5.3 Prescaler                          | V-19  |

| 5.3.1 Prescaler Operation              | V-19  |

| 5.3.2 Setup Example                    |       |

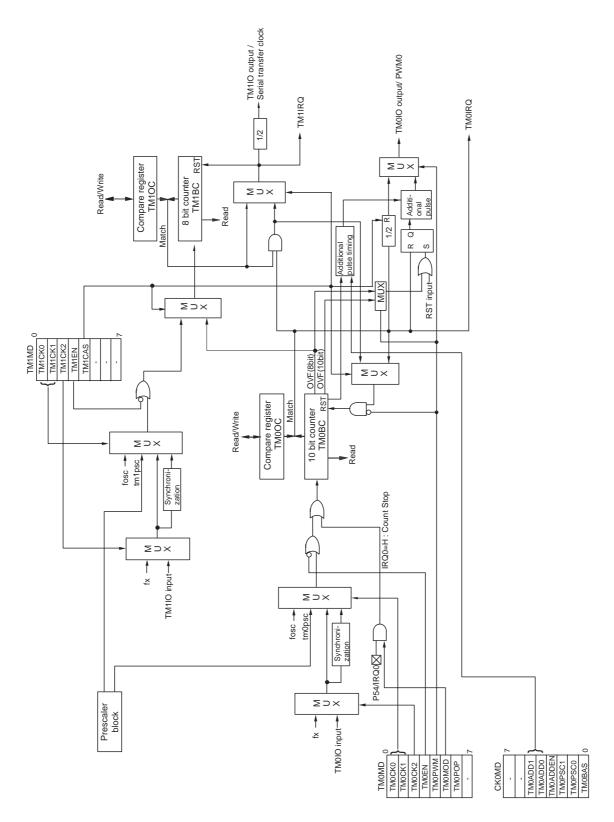

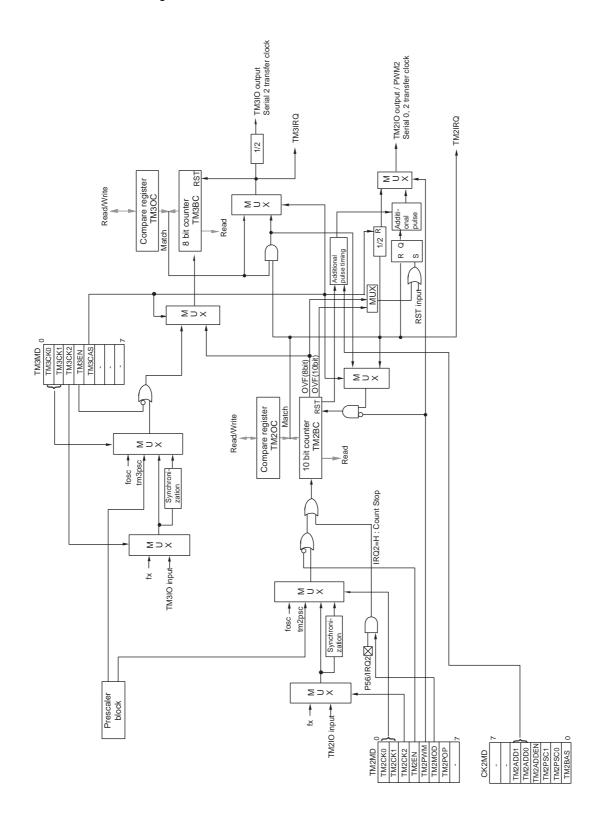

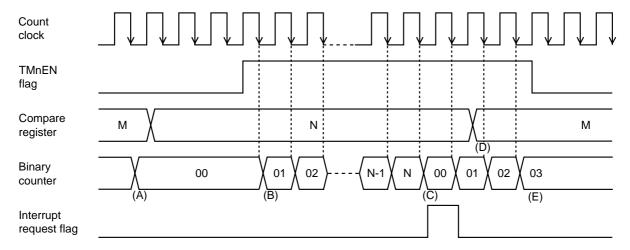

| 5.4 8-bit Timer                        | V-21  |

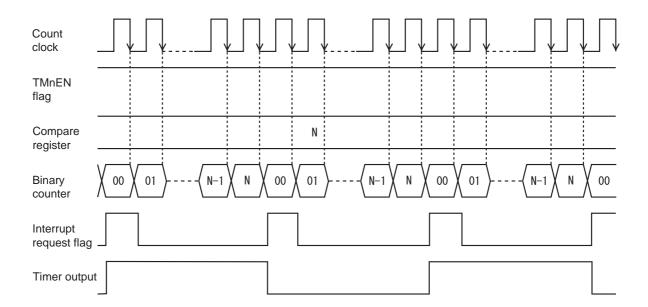

| 5.4.1 8-bit Timer Operation            | V-21  |

| 5.4.2 Setup Example                    | V-24  |

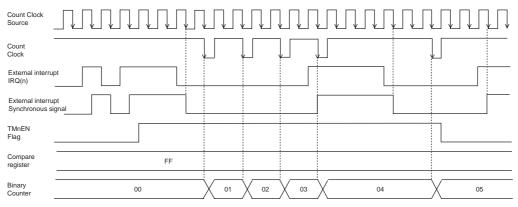

| 5.5 8-bit Event Count                  | V-26  |

| 5.5.1 Operation                        | V-26  |

| 5.5.2 Setup Example                    | V-29  |

| 5.6 8-bit Timer Pulse Output           | V-31  |

| 5.6.1 Operation                        | V-31  |

| 5.6.2 Setup Example                    | V-32  |

| 5.7 8-bit PWM Output                   | V-34  |

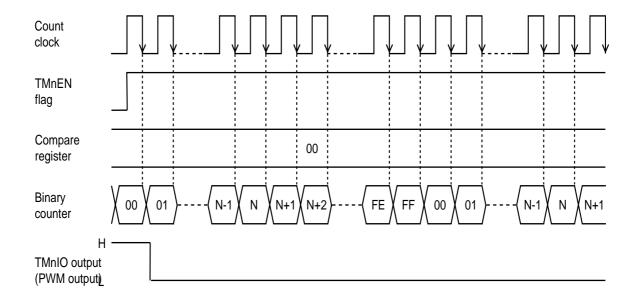

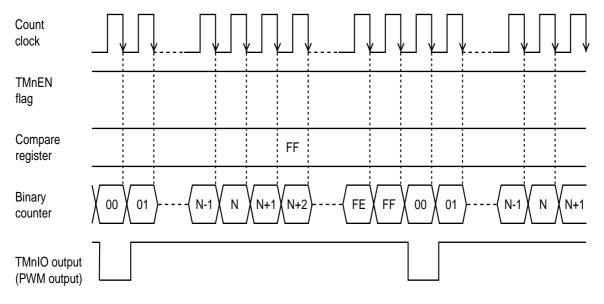

| 5.7.1 Operation                        | V-34  |

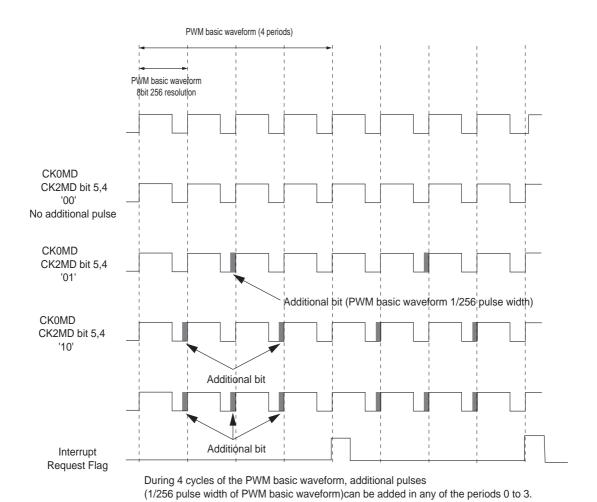

| 5.7.2 PWM Output with Additional Pulse | V-37  |

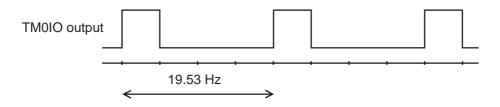

| 5.7.3 Setup Example                    | V-39  |

| 5.8 Serial Transfer Clock Output       | V-41  |

| 5.8.1 Operation                        | V-41  |

| 5.8.2 Setup Example                    | V-42  |

| 5.9 Simple Pulse Width Measurement     | V-43  |

| 5.9.1 Operation                        | V-43  |

| 5.9.2 Setup Example                    | V-44  |

| 5.10 Cascade Connection                | V-46  |

| 5.10.1 Operation                       |       |

| 5.10.2 Setup Example                   | V-48  |

|                                        |       |

| Chapter 6 16-bit Timers                | VI-1  |

| 6.1 Overview                           |       |

| 6.1.1 Functions                        | VI-2  |

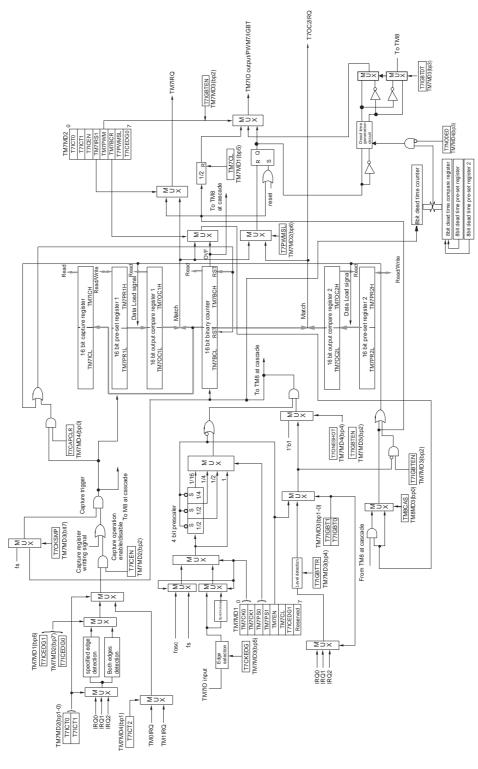

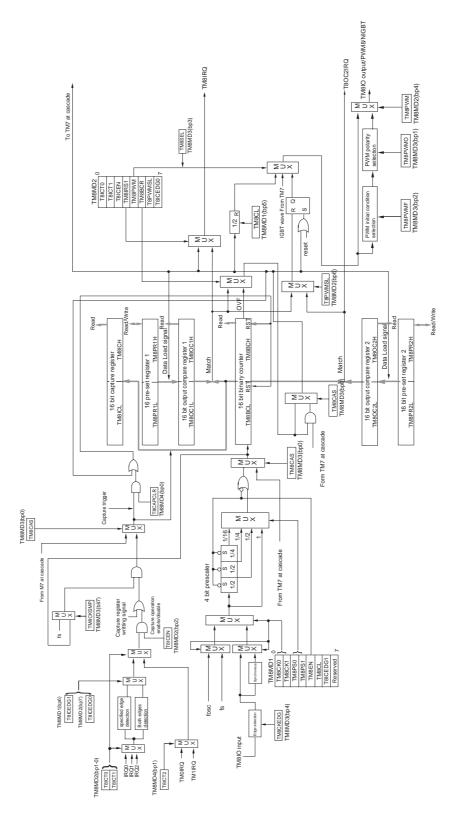

| 6.1.2 Block Diagram                    | VI-4  |

| 6.2 Control Registers                  |       |

| 6.2.1 Registers                        |       |

| 6.2.2 Programmable Timer Registers     |       |

| 6.2.3 Timer Mode Registers             | VI-16 |

| 6.3 Operation                          |       |

| 6.3.1 Operation                        | VI-24 |

| 6.3.2 Setup Example                                                             | VI-28 |

|---------------------------------------------------------------------------------|-------|

| 6.4 16-bit Event Count                                                          | VI-29 |

| 6.4.1 Operation                                                                 |       |

| 6.4.2 Setup Example                                                             |       |

| 6.5 16-bit Timer Pulse Output                                                   | VI-35 |

| 6.5.1 Operation                                                                 | VI-35 |

| 6.5.2 Setup Example                                                             | VI-37 |

| 6.6 16-bit Standard PWM Output (Only duty can be changed consecutively)         | VI-39 |

| 6.6.1 Operation                                                                 | VI-39 |

| 6.6.2 Setup Example                                                             | VI-42 |

| 6.7 16-bit High Precision PWM Output (Cycle/Duty can be changed consecutively)  | VI-44 |

| 6.7.1 Operation                                                                 | VI-44 |

| 6.7.2 Setup Example                                                             | VI-47 |

| 6.8 16-bit Timer Capture                                                        |       |

| 6.8.1 Operation                                                                 | VI-49 |

| 6.8.2 Setup Example                                                             | VI-55 |

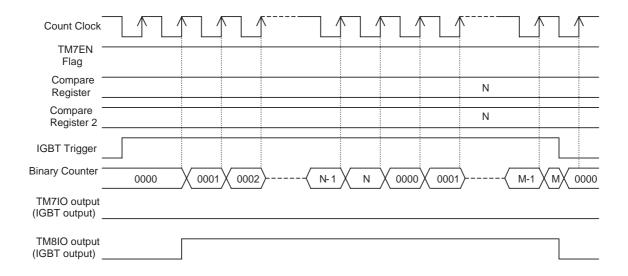

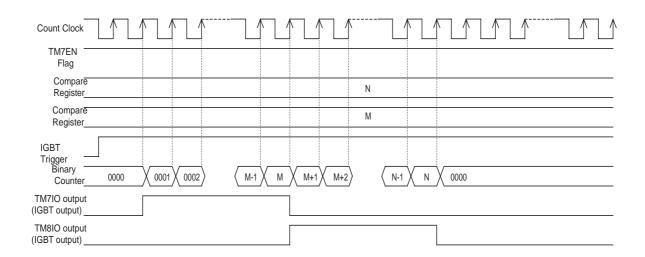

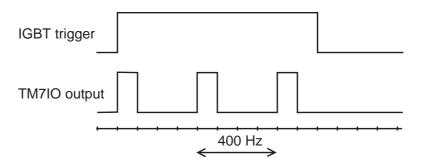

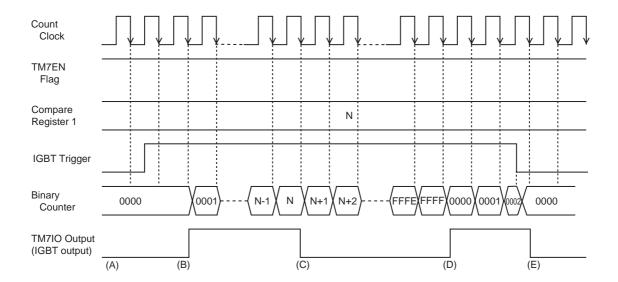

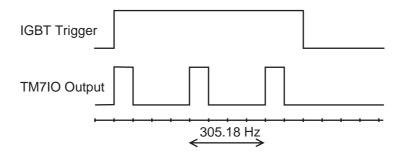

| 6.9 16-bit High Precision IGBT Output (Cycle/Duty can be changed consecutively) | VI-57 |

| 6.9.1 Operation                                                                 | VI-57 |

| 6.9.2 Setup Example                                                             | VI-62 |

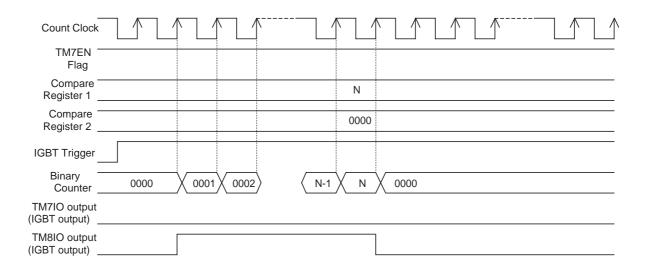

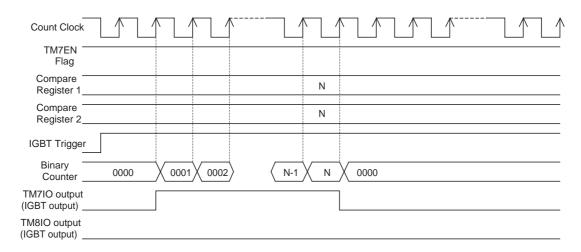

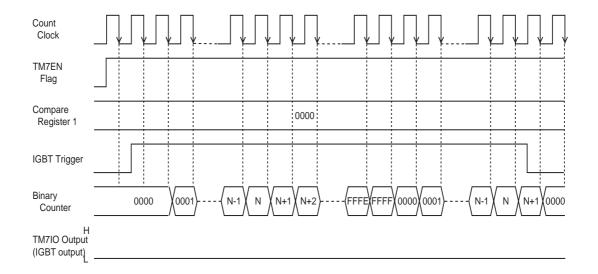

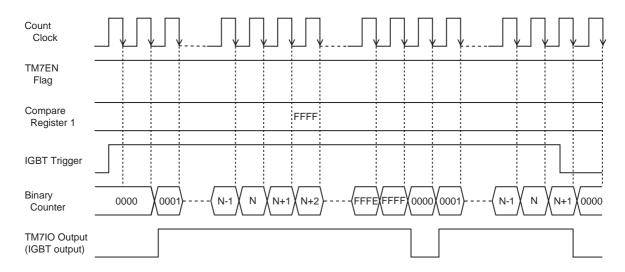

| 6.10 16-bit Standard IGBT Output (Only duty can be changed consecutively)       |       |

| 6.10.1 Operation                                                                |       |

| 6.10.2 Setup Example                                                            | VI-70 |

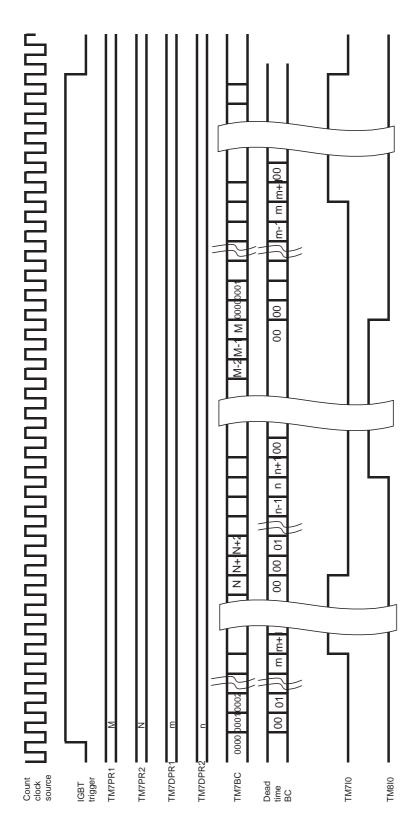

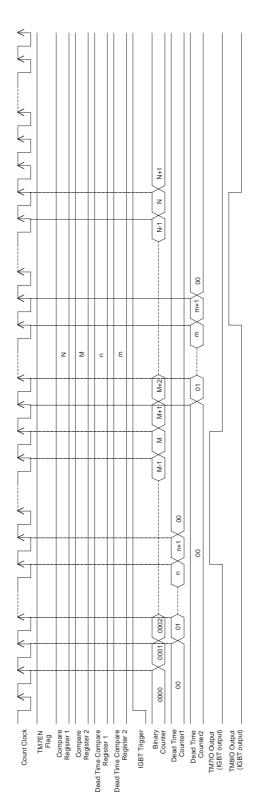

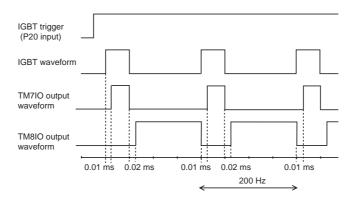

| 6.11 Dead Time IGBT Output                                                      |       |

| 6.11.1 Operation                                                                |       |

| 6.11.2 Setup Example                                                            | VI-76 |

| 6.12 16-bit Timer Cascade Connection                                            | VI-79 |

| 6.12.1 Operation                                                                | VI-79 |

| 6.12.2 Setup Example (Timer Operation)                                          | VI-81 |

| 6.12.3 Setup Example (PWM Operation)                                            | VI-83 |

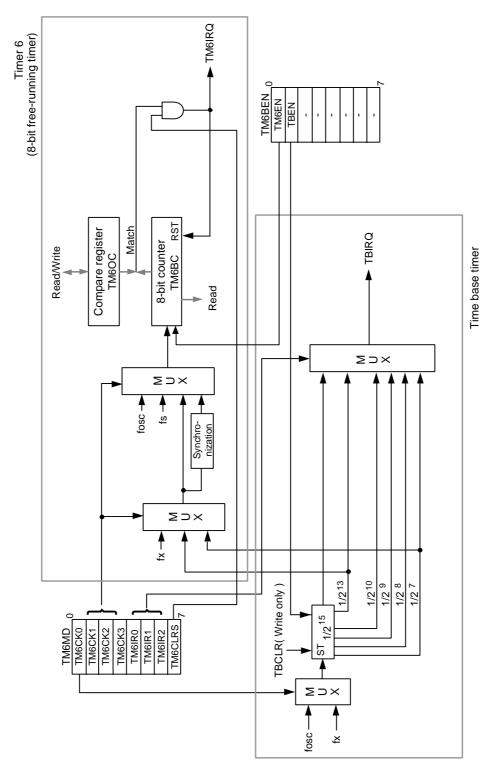

| Chapter 7 Time Base Timer / Free-running Timer                                  | VII-1 |

| 7.1 Overview                                                                    | VII-2 |

| 7.1.1 Functions                                                                 | VII-2 |

| 7.1.2 Block Diagram                                                             | VII-4 |

| 7.2 Control Registers                                                           | VII-5 |

| 7.2.1 Control Registers                                                         | VII-5 |

| 7.2.2 Programmable Timer Registers                                              | VII-6 |

| 7.2.3 Timer 6 Enable Registers                                                  |       |

| 7.2.4 Timer Mode Registers                                                      | VII-8 |

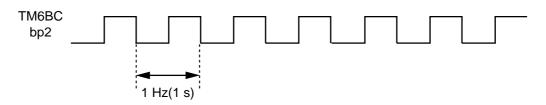

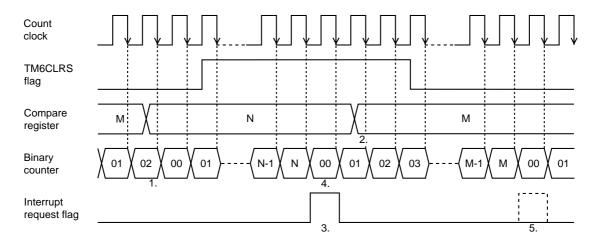

| 7.3 8-bit Free-running Timer                                         | VII-9  |

|----------------------------------------------------------------------|--------|

| 7.3.1 Operation                                                      | VII-9  |

| 7.3.2 Setup Example                                                  | VII-13 |

| 7.4 Time Base Timer                                                  | VII-15 |

| 7.4.1 Operation                                                      |        |

| 7.4.2 Setup Example                                                  |        |

| · · · · · · · · · · · · · · · · · · ·                                |        |

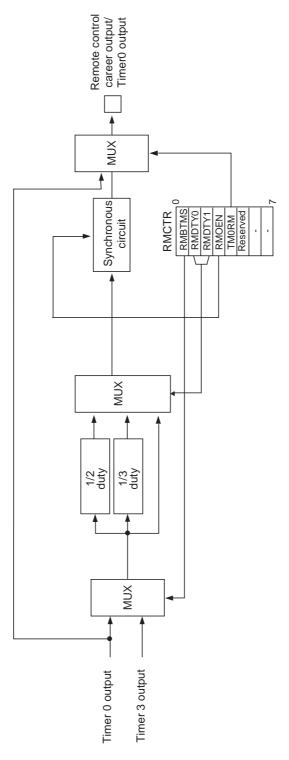

| Chapter 8 Remote Control Carrier Functions                           | VIII-1 |

| 8.1 Overview                                                         | VIII-2 |

| 8.1.1 Functions                                                      | VIII-2 |

| 8.1.2 Block Diagram                                                  | VIII-3 |

| 8.2 Control Registers                                                | VIII-4 |

| 8.2.1 Control Registers                                              |        |

| 8.2.2 Remote Control Carrier Output Control Register                 |        |

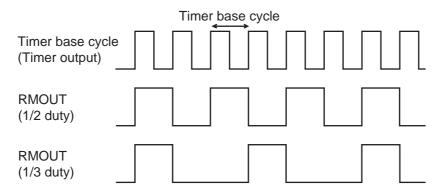

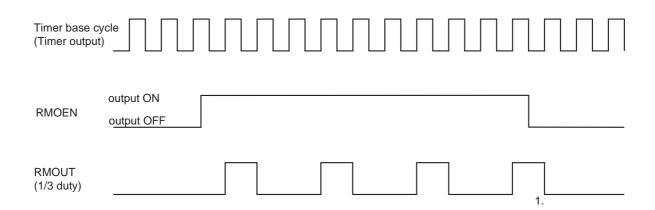

| 8.3 Operations                                                       | VIII-6 |

| 8.3.1 Operations                                                     |        |

| 8.3.2 Setup Examples                                                 |        |

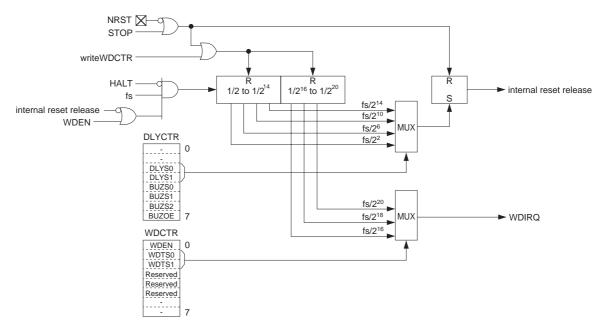

| Chapter 9 Watchdog Timer                                             | IX-1   |

| 9.1 Overview                                                         | IX-2   |

| 9.1.1 Functions                                                      | IX-2   |

| 9.1.2 Block Diagram                                                  | IX-3   |

| 9.2 Control Register                                                 | IX-4   |

| 9.2.1 Control Registers                                              |        |

| 9.2.2 Watchdog Timer Control Register                                |        |

| 9.3 Operation                                                        | IX-5   |

| 9.3.1 Operation                                                      | IX-5   |

| 9.3.2 Setup Example                                                  | IX-7   |

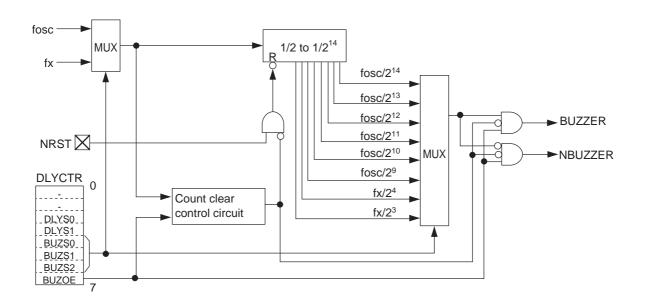

| Chapter 10 Buzzer                                                    | X-1    |

| 10.1 Overview                                                        | X-2    |

| 10.1.1 Functions                                                     |        |

| 10.1.2 Block Diagram                                                 |        |

| 10.2 Control Register                                                | X-4    |

| 10.2.1 Registers                                                     |        |

| 10.2.2 Oscillation Stabilization Wait Time Control Register (DLYCTR) |        |

| 10.3 Operation                                                       | X-6    |

| 10.3.1 Operation                          | X-6    |

|-------------------------------------------|--------|

| 10.3.2 Setup Example                      |        |

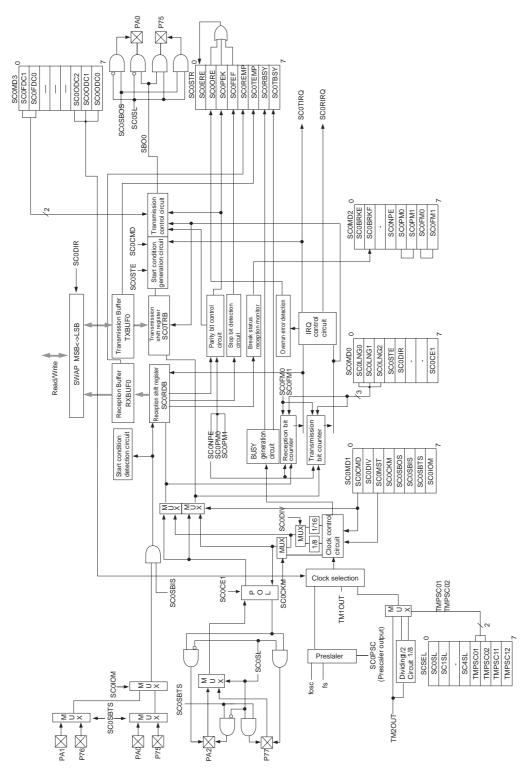

| Chapter 11 Serial interface 0             | XI-1   |

| -<br>11.1 Overview                        | VI 9   |

| 11.1 Functions                            |        |

| 11.1.2 Block Diagram                      |        |

| 11.2 Control Registers                    | VI 5   |

| 11.2.1 Registers                          |        |

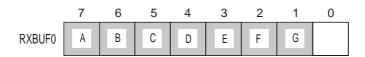

| 11.2.2 Data Buffer Registers              |        |

| 11.2.3 Mode Registers                     |        |

| 11.3 Operation                            | XI-13  |

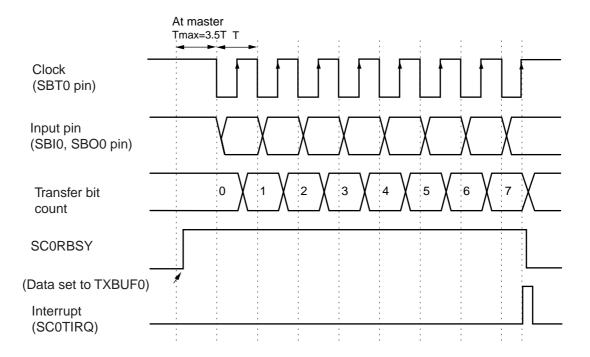

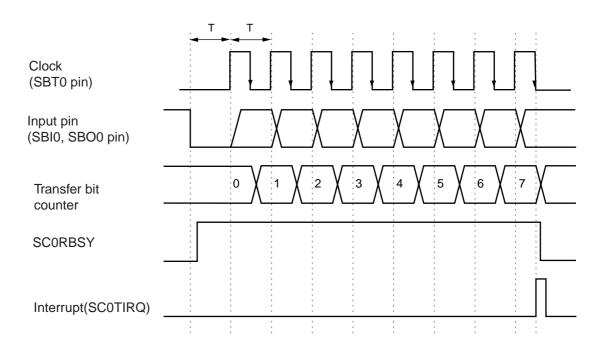

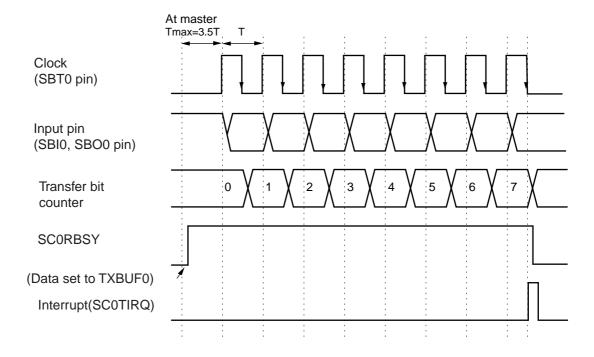

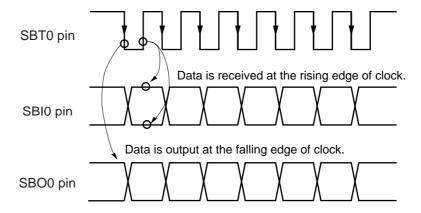

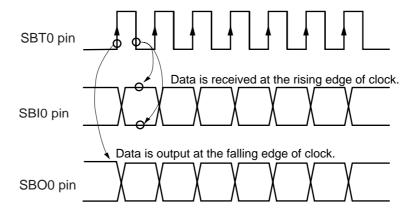

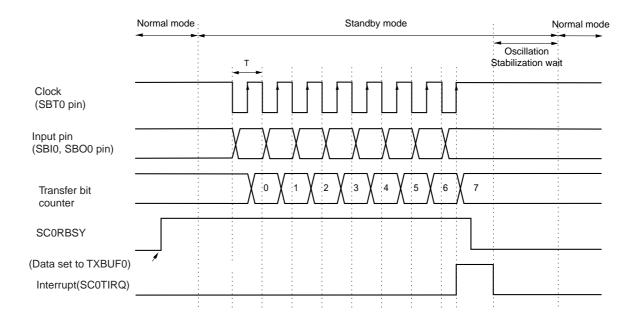

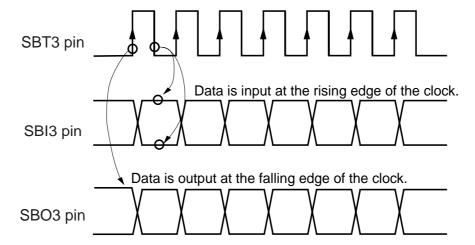

| 11.3.1 Clock Synchronous Serial Interface |        |

| 11.3.2 Setup Example                      |        |

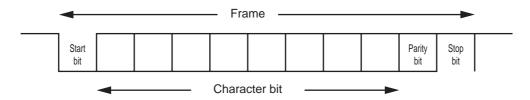

| 11.3.3 UART Serial Interface              |        |

| 11.3.4 Setup Example                      | XI-60  |

| Chapter 12 Serial interface 1             | XII-1  |

| 12.1 Overview                             | XII-2  |

| 12.1.1 Functions                          | XII-2  |

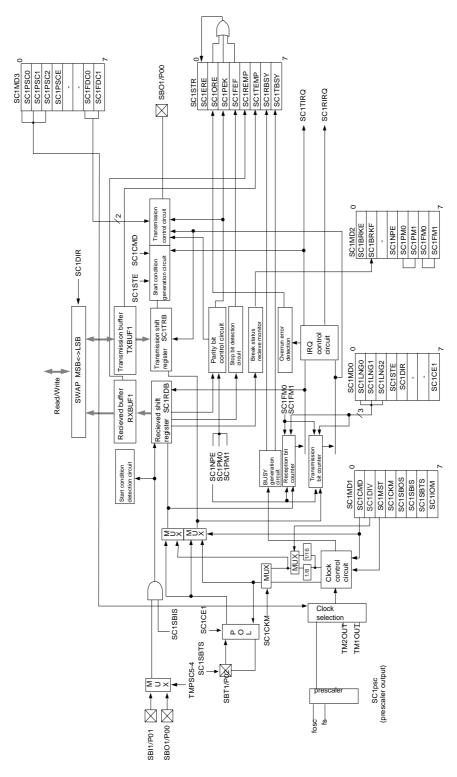

| 12.1.2 Block Diagram                      | XII-4  |

| 12.2 Control Registers                    | XII-5  |

| 12.2.1 Registers                          | XII-5  |

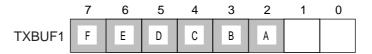

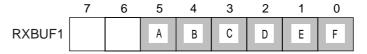

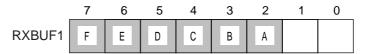

| 12.2.2 Data Buffer Registers              | XII-6  |

| 12.2.3 Mode Registers                     | XII-7  |

| 12.3 Operation                            | XII-13 |

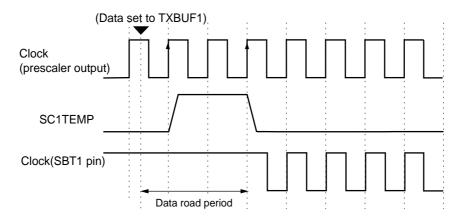

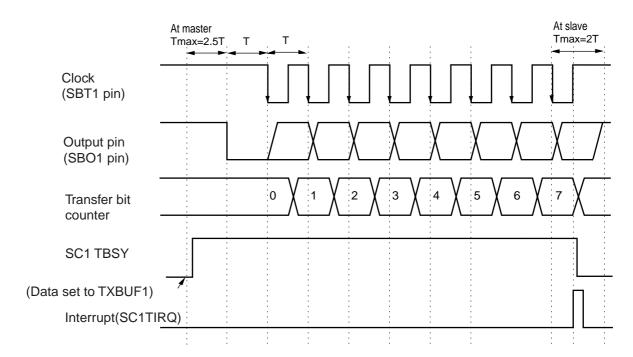

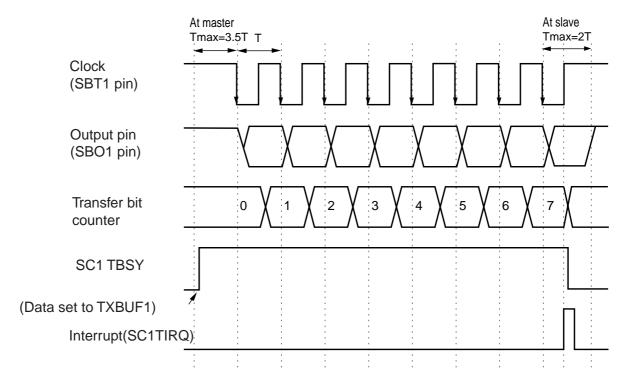

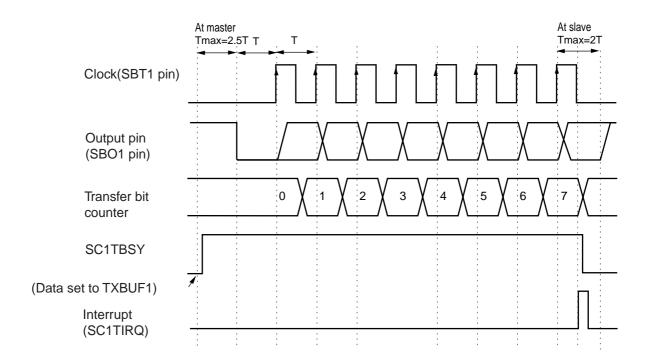

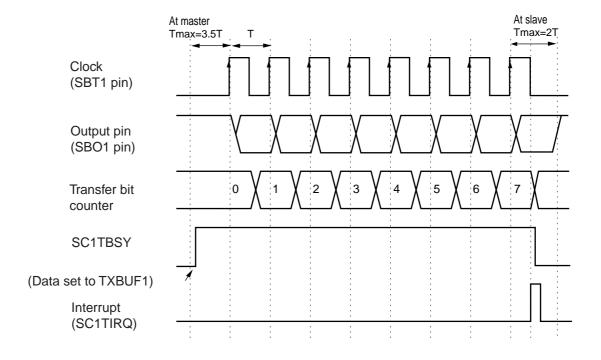

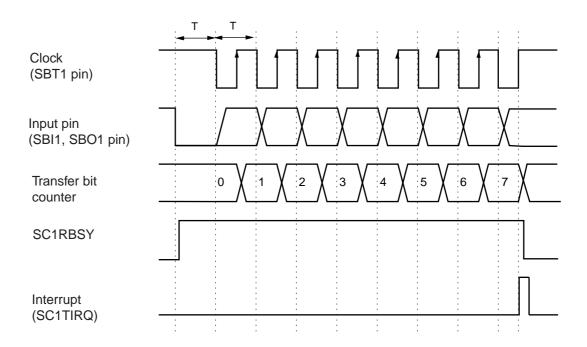

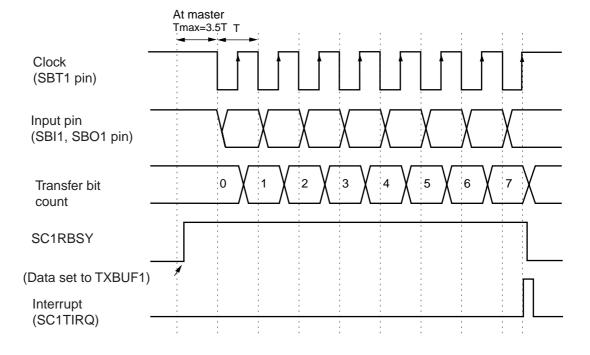

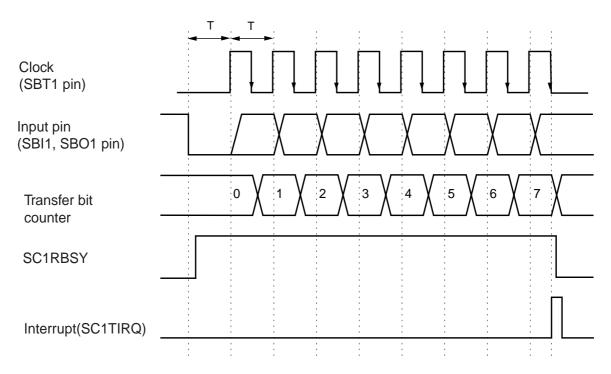

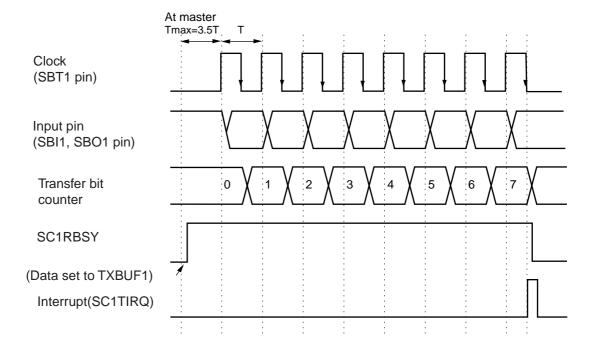

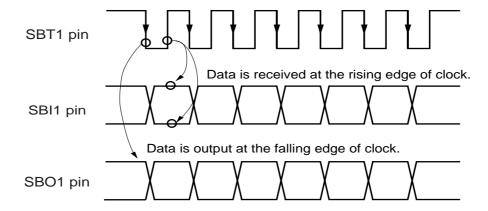

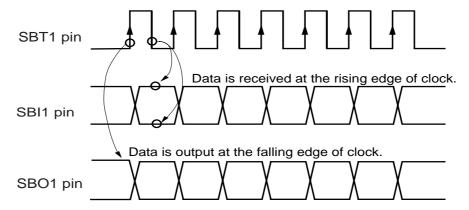

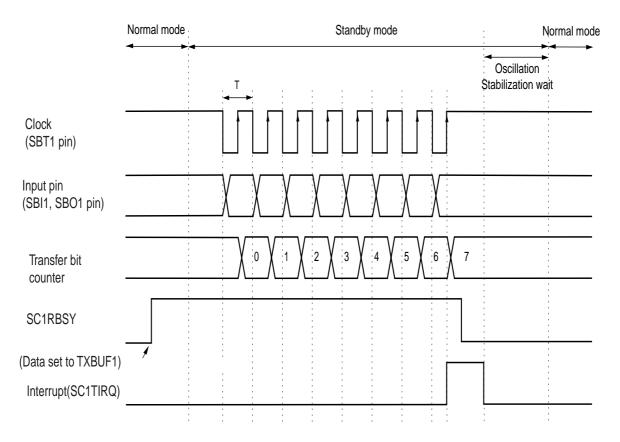

| 12.3.1 Clock Synchronous Serial Interface | XII-13 |

| 12.3.2 Setup Example                      | XII-33 |

| 12.3.3 UART Serial Interface              | XII-42 |

| 12.3.4 Setup Example                      | XII-59 |

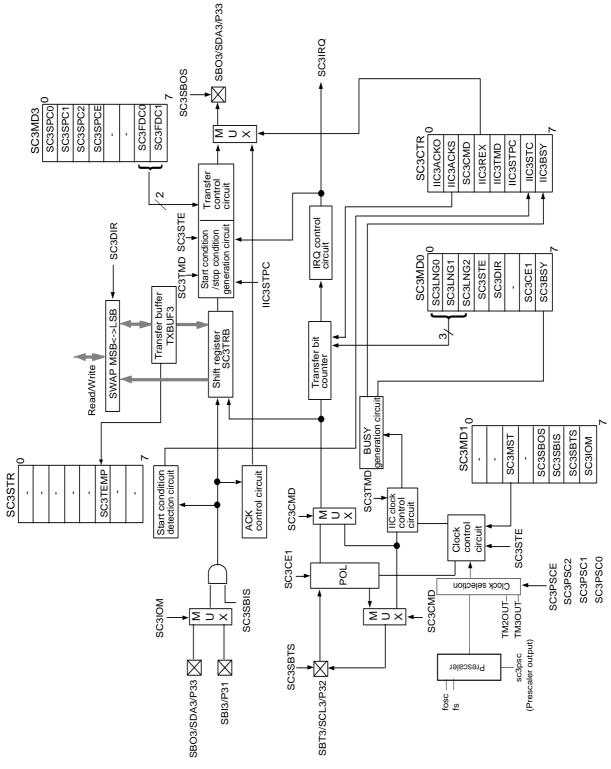

| Chapter 13 Serial Interface 3             | XIII-1 |

| 13.1 Overview                             | XIII-2 |

| 13.1.1 Functions                          |        |

| 13.1.2 Block Diagram                      |        |

| 13.2 Control Registers                    | XIII-4 |

| 13.2.1 Registers List                     |        |

| 13.2.2 Data Buffer Register               |        |

| 13.2.3 Data Register                      | XIII-5 |

| 13.2.4 Serial interface 3 Mode Register                | XIII-6  |

|--------------------------------------------------------|---------|

| 13.3 Operation                                         | XIII-11 |

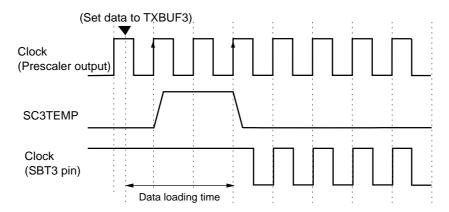

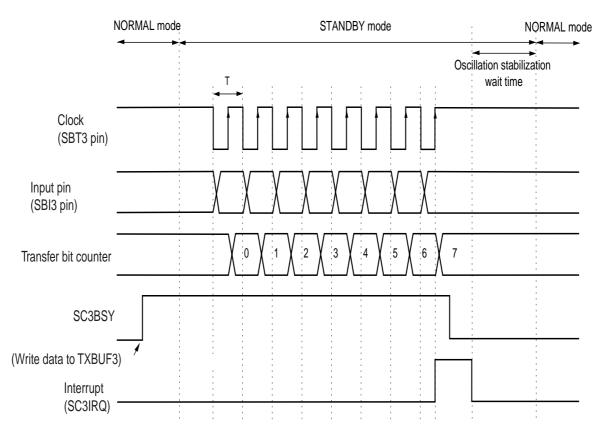

| 13.3.1 Clock Synchronous Serial Interface              | XIII-11 |

| 13.3.2 Setup Example                                   | XIII-28 |

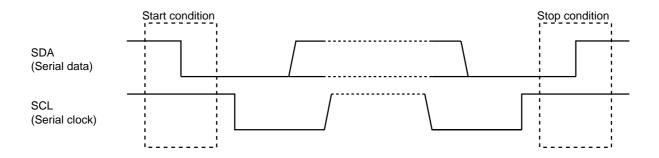

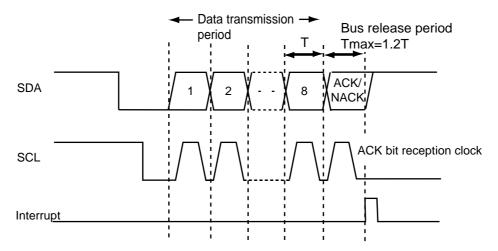

| 13.3.3 Single Master IIC Serial Interface              | XIII-37 |

| 13.3.4 Setup Example                                   |         |

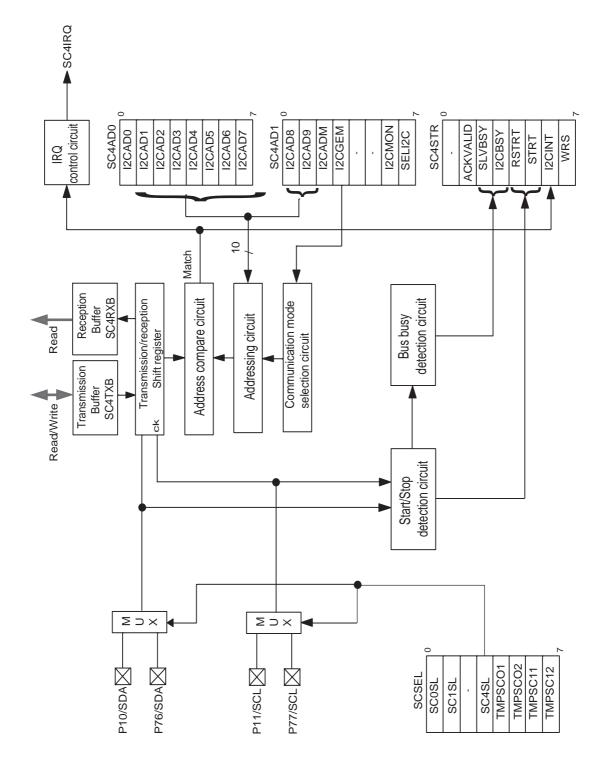

| Chapter 14 Serial Interface 4                          | XIV-1   |

| 14.1 Overview                                          | XIV-2   |

| 14.1.1 Functions                                       | XIV-2   |

| 14.1.2 Block Diagram                                   | XIV-3   |

| 14.1.3 Control Registers                               | XIV-4   |

| 14.1.4 Data Buffer Register                            | XIV-5   |

| 14.1.5 Mode Register                                   | XIV-6   |

| 14.2 Operation                                         | XIV-9   |

| 14.2.1 Setup Example of the Slave IIC Serial Interface | XIV-11  |

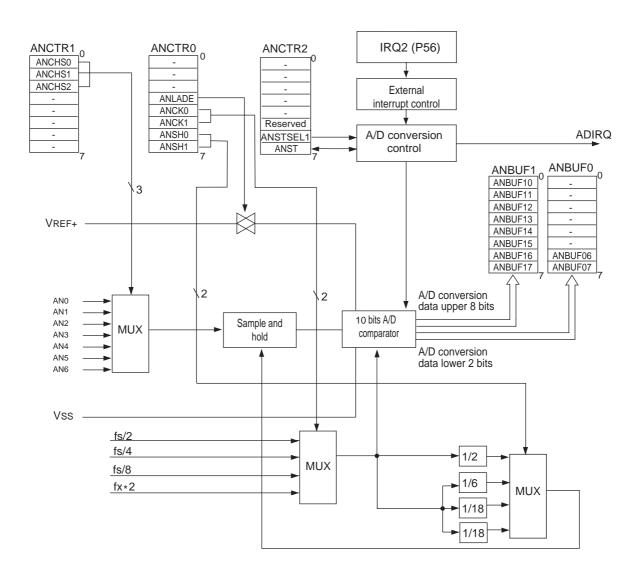

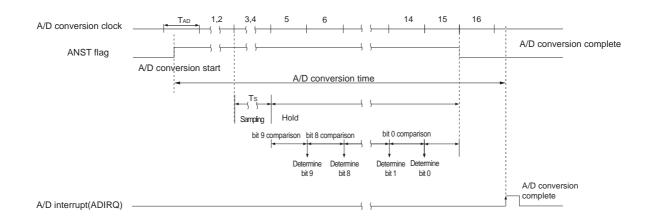

| Chapter 15 A/D Converter                               | XV-1    |

| 15.1 Overview                                          | XV-2    |

| 15.1.1 Functions                                       |         |

| 15.1.2 Block Diagram                                   |         |

| 15.2 Control Registers                                 | XV-4    |

| 15.2.1 Registers                                       | XV-4    |

| 15.2.2 Control Registers                               | XV-5    |

| 15.2.3 Data Buffers                                    | XV-7    |

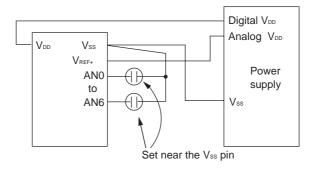

| 15.3 Operation                                         | XV-8    |

| 15.3.1 Setup                                           | XV-10   |

| 15.3.2 Setup Example                                   | XV-12   |

| 15.3.3 Cautions                                        | XV-14   |

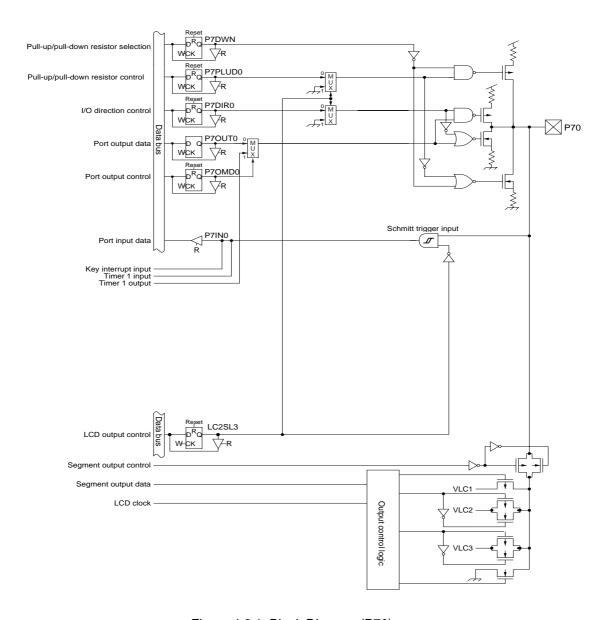

| Chapter 16 LCD                                         | XVI-1   |

| 16.1 Functions                                         | XVI-2   |

| 16.1.1 Functions                                       | XVI-2   |

| 16.1.2 LCD Operation in Standby Mode                   | XVI-3   |

| 16.1.3 Maximum Pixels                                  | XVI-4   |

| 16.1.4 Switching I/O ports and LCD segment pins        | XVI-4   |

| 16.1.5 Switching I/O Ports and LCD Voltage¶            | XVI-4   |

| 16.1.6 Block Diagram                                   | XVI-5   |

| 16.2 Control Registers                                 | XVI-6   |

| 16.2.1 Registers                                 | XVI-6   |

|--------------------------------------------------|---------|

| 16.2.2 Mode Control Register 1 (LCDMD1)          | XVI-7   |

| 16.2.3 Mode Control Register 2 (LCDMD2)          | XVI-8   |

| 16.2.4 Output Control Register 1 (LCCTR1)        | XVI-9   |

| 16.2.5 Output Control Register 2 (LCCTR2)        | XVI-10  |

| 16.2.6 Output Control Register 3 (LCCTR3)        | XVI-11  |

| 16.2.7 Segment Output Latch                      | XVI-12  |

| 16.3 Operation                                   | XVI-13  |

| 16.3.1 Operation                                 | XVI-13  |

| 16.3.2 Power Supply                              | XVI-14  |

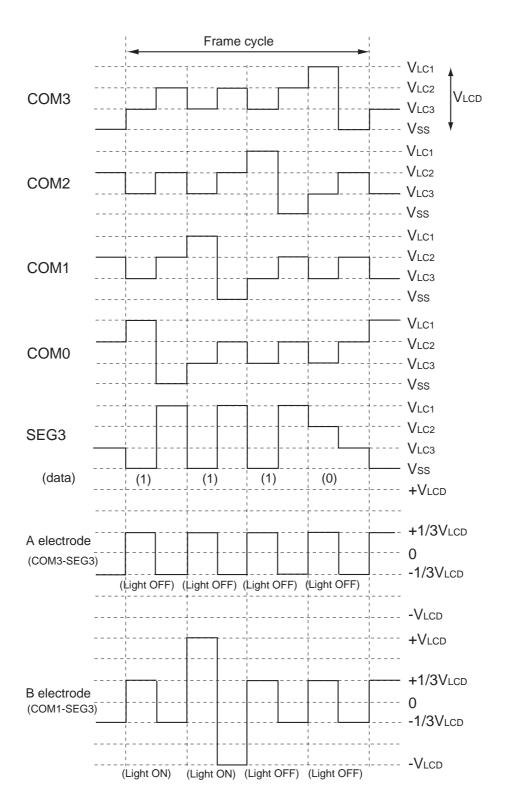

| 16.3.3 Frame Cycle                               | XVI-19  |

| 16.3.4 Setup Example of the LCD Driver Circuit   | XVI-20  |

| 16.4 Display                                     | XVI-21  |

| 16.4.1 Static                                    | XVI-21  |

| 16.4.2 Setup Example (Static)                    | XVI-23  |

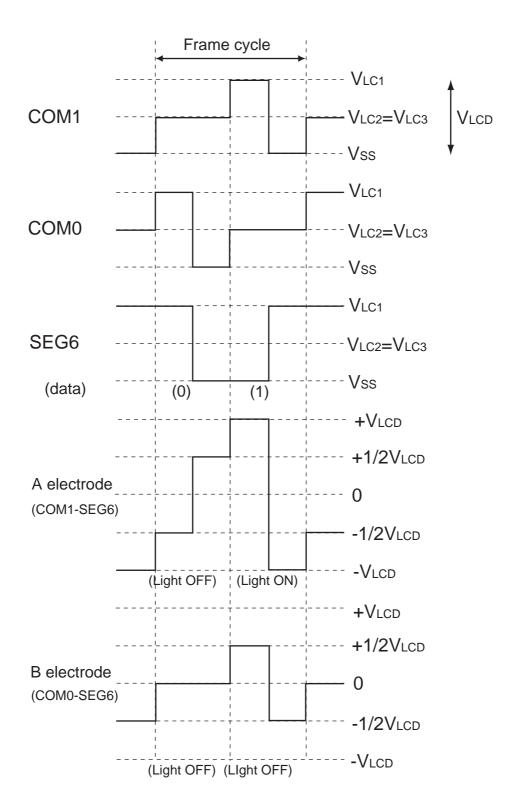

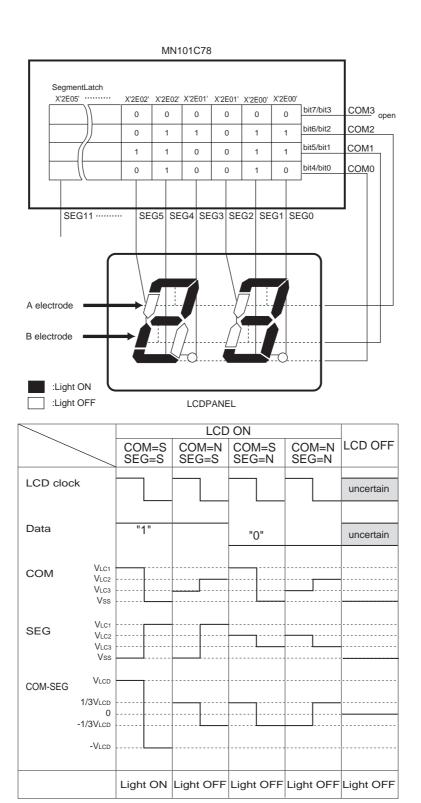

| 16.4.3 1/2duty                                   | XVI-24  |

| 16.4.4 Setup Example (1/2 duty)                  | XVI-26  |

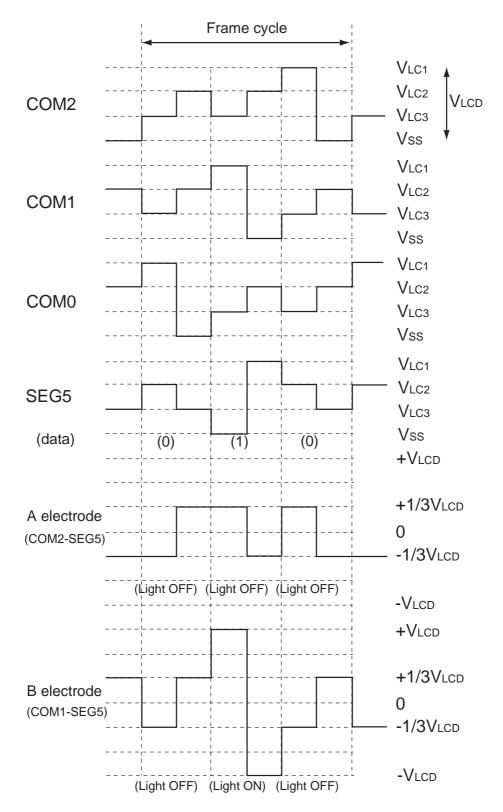

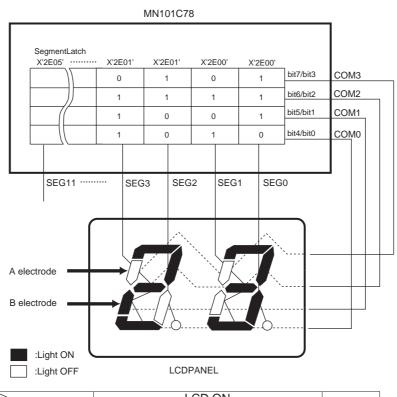

| 16.4.5 1/3 duty                                  | XVI-27  |

| 16.4.6 Setup Example (1/3 duty)                  |         |

| 16.4.7 1/4 duty                                  | XVI-30  |

| 16.4.8 Setup Example (1/4 duty)                  | XVI-32  |

| Chapter 17 Appendix                              | XVII-1  |

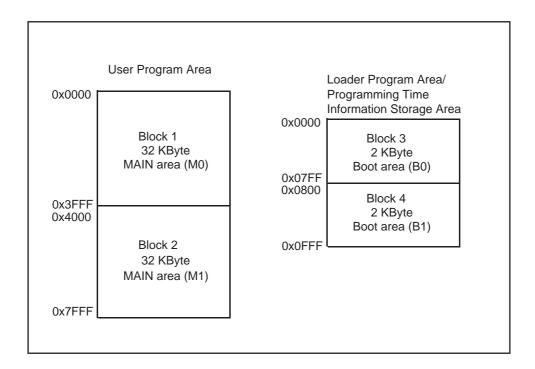

| 17.1 Flash EEPROM                                | XVII-2  |

| 17.1.1 Overview                                  | XVII-2  |

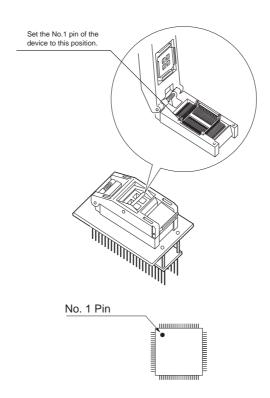

| 17.2 PROM Writer Mode                            | XVII-4  |

| 17.2.1 Overview                                  | XVII-4  |

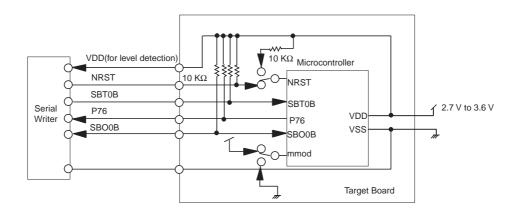

| 17.3 Onboard Serial Programming Mode             | XVII-5  |

| 17.3.1 Overview                                  | XVII-5  |

| 17.3.2 Circuit Requirements for the Target Board | XVII-6  |

| 17.3.3 Built-in Hardware for Onboard Programming | XVII-7  |

| 17.3.4 MN101CF78A Clock on the Target Board      | XVII-8  |

| 17.4 Special Function Registers List             | XVII-9  |

| 17.5 Instruction Set                             | XVII-28 |

| 17.6 Instruction Map                             | XVII-34 |

# Chapter 1 Overview

### 1.1 Overview

#### 1.1.1 Overview

The MN101C series of 8-bit single-chip microcomputers incorporate multiple types of peripheral functions. This chip series is well suited for camera, VCR, MD, TV, CD, LD, printer, telephone, home automation, pager, air conditioner, PPC, remote control, fax machine, music instrument and other applications.

This LSI brings to embedded microcomputer applications flexible, optimized hardware configurations and a simple efficient instruction set. The MN101C78A has an internal 32 KB of ROM and 1.5 KB of RAM. Peripheral functions include 4 external interrupts, 18 internal interrupts including NMI, 9 timer counters, 4 sets of serial interfaces, A/D converter, watchdog timer, buzzer output, and remote control output. The configuration of this microcomputer is well suited for application as a system controller in a camera, timer selector for VCR, CD player, or MD.

With two oscillation system (max. 10 MHz/32 kHz) contained on the chip, the system clock can be switched to high frequency input (high speed mode), or to low frequency input (low speed mode).

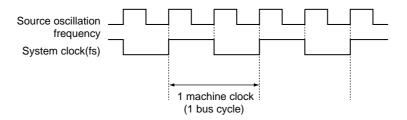

The system clock is generated by dividing the oscillation clock. The best operation clock for the system can be selected by switching its frequency by software. High speed mode has the normal mode which is based on 2-cycle clock (fosc/2) and the double speed mode which is based on the same cycle clock with fosc.

A machine cycle (min. instructions execution) in the normal mode is 250 ns when fosc is 8 MHz, and when fosc is 10 MHz, a machine cycle is 200 ns. A machine cycle in the double speed mode is 125 ns when fosc is 8 MHz, and 100 ns when fosc is 10 MHz. Two types of packages are available, 48-pin TQFP and 44-pin QFP.

### 1.1.2 Product Summary

This manual describes the following models of the MN101C78 series. These products have identical functions. However, MN101C78A is described mainly.

Table:1.1.1 Product Summary

| Model        | ROM Size | RAM Size | Classification       |

|--------------|----------|----------|----------------------|

| MN101C78A*1  | 32 KB    | 1.5 KB   | Mask ROM version     |

| MN101C789*2  | 24 KB    | 1.5 KB   | Mask ROM version     |

| MN101CF78A*1 | 32 KB    | 1.5 KB   | Flash EEPROM version |

- 1 Under development

- \*2 Under consideration

## 1.2 Hardware Functions

#### Functions

ROM capacity: 32768x8 bit \*1

RAM capacity: 1536x8 bit \*1

\*1 Differs depending upon the model. Refer to [Chapter 1 1-1-2 Product Summary]

- Package: QFP44 (10 mm square, 0.8 mm pitch)

TQFP48 (7 mm square, 0.5 mm pitch)

- Machine cycle: High speed mode <fs=fosc/2, fosc/1>

0.125 ms / -, 8 MHz (2.7 V to 3.6 V)

0.25 ms / 8 MHz, 4 MHz (2.3 V to 3.6 V) \*2  $\,$

0.50 ms / 4 MHz, 2 MHz (1.8 V to 3.6 V)  $^{*}$ 2

Low speed mode <fs=fx / 2>

62.5 ms / 32 kHz (1.8 V to 3.6 V) \*2

\*2 The guaranteed operating range for Flash EEPROM version MN1010CF78A is 2.7 V to 3.6 V.

- Internal clock gear: Operation speed of internal system clock is variable by changing the frequency.

(2, 4, 16, 32, 64, 128 dividing)

- Oscillating circuit: Two oscillation circuits (high speed / low speed)

- Operation modes: NORMAL mode

SLOW mode HALT mode STOP mode

(The operation clock can be switched in each model)

- Operating voltage: 1.8 V to 3.6 V (Flash version of TQFP48, MN101CF78A is 2.7 V to 3.6 V)

- Operating temperature: -40 C to +85 C

- Interrupt: 22 levels

<External interrupts> Edge selectable.

IRQ0: External interrupt (AC zero cross detector. With/Without noise filter)

IRQ1: External interrupt (AC zero cross detector. With/Without noise filter)

IRQ2: External interrupt (Both edges selectable IRQ3 – external interrupt)

IRQ3: (Key scan interrupt only)

<Timer interrupts> TM0IRQ: Timer 0 interrupt (8-bit timer)

TM1IRQ: Timer 1 interrupt (8-bit timer)

TM2IRQ: Timer 2 interrupt (8-bit timer)

TM3IRQ: Timer 3 interrupt (8-bit timer)

TM7IRQ: Timer 7 interrupt (16-bit timer)

T7OC2IRQ: Timer 7 compare register 2 interrupt (16-bit timer)

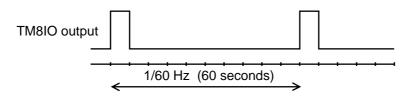

TM8IRQ: Timer 8 interrupt (16-bit timer)

T8OC2IRQ: Timer 8 compare register 2 interrupt (16-bit timer)

TM6IRQ: Timer 6 interrupt (8-bit timer)

TBIRQ: Time base timer interrupt

#### <Serial interface interrupts>

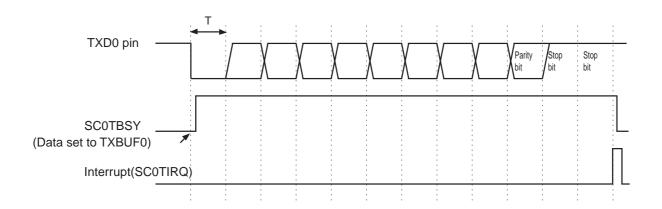

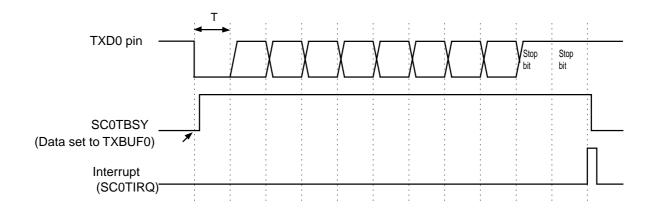

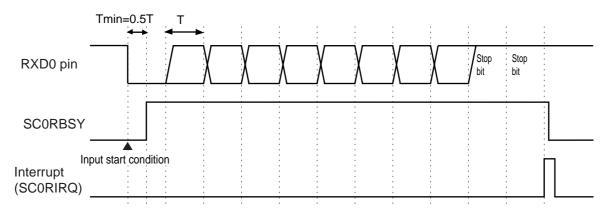

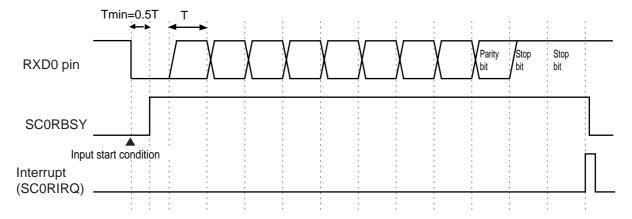

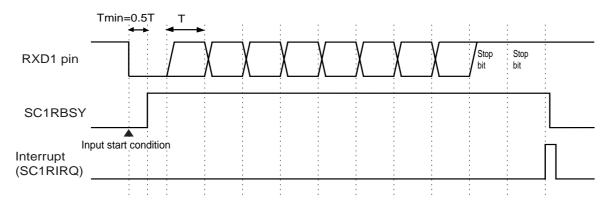

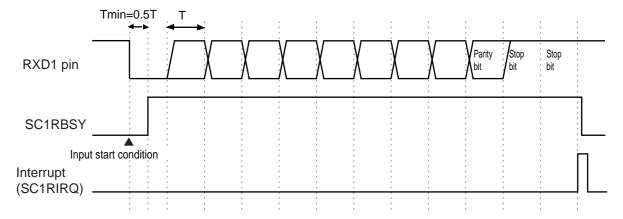

SC0RIRQ: Serial interface 0 interrupt (UART reception)

SC0TIRQ: Serial interface 0 interrupt (UART transmission, synchronous)

SC1RIRQ: Serial interface 1 interrupt (UART reception)

${\tt SC1TIRQ: Serial\ interface\ 1\ interrupt\ (UART\ transmission,\ synchronous)}$

SC3IRQ: Serial interface 3 interrupt (Single master IIC, synchronous)

SC4IRQ: Serial interface 4 interrupt (Slave IIC)

<Watchdog timer interrupt> NMI: Non-maskable interrupt

<A/D conversion end interrupt> ADIRQ: A/D conversion interrupt

- A/D converter: 10-bit x 7 channels

- Timer counter: 9 timers All timer counters generate interrupt

Timer 0 (8-bit timer for general use)

Square wave output, PWM output, Event count, Simple pulse width measurement,

Clock source: fosc, fosc/4, fosc/16, fosc/32, fosc/64, fs/2, fs/4, fx, external clock

P50 of the large current pin (TM0OA) or P15 (TM0OB) for PWM output

Timer 1 (8-bit timer for general use or UART baud rate timer)

Square wave output, Event count, Cascade connection to timer 0

Clock source: fosc, fosc/4, fosc/16, fosc/64, fosc/128, fs/2, fs/8, fx, external clock

Timer 2 (8-bit timer for general use or UART baud rate timer)

Square wave output, PWM output, Event count, Simple pulse width measurement

Clock source: fosc, fosc/4, fosc/16, fosc/32, fosc/64, fs/2, fs/4, fx, external clock

Added pulse (2-bit) system PWM

P52 of the large current pin (TM2OA) or P16 (TM2OB) for PWM output

Timer 3 (8-bit timer for general use)

Square wave output, Event count,

Cascade connection to timer2

Clock source: fosc, fosc/4, fosc/16, fosc/64, fosc/128, fs/2, fs/8, fx, external clock

Timer 6 (8-bit timer for general use)

Combined with time base timer, it can be set to measure one minute intervals.

Clock source: fosc, fs, fx, time base output (1/2<sup>12</sup> or 1/2<sup>13</sup>)

Timer 7 (16-bit timer for general use)

Square wave output, P51 of the large-current pin (TM7O) for PWM output and IGBT control output (Duty/Cycle continuous variable), Event count, Pulse width measurement, Input capture, Cascade connection to timer 8 (32-bit timer, 32-bit PWM, input capture can be used)

Clock source: 1/1, 1/2, 1/4, 1/16 of any one of fosc, fx, or external clock

Timer 8 (16-bit timer double buffering)

Square wave output, P53 of the large-current pin (TM8O) for PWM output (Duty continuous variable), Event count, pulse width measurement, Input capture

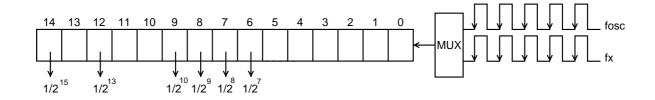

Time base timer

Clock source: fosc, fx

Interrupt enable for source clock at the dividing output of 1/27, 1/28, 1/29, 1.210, 1/213, 1/215

Watchdog timer

Watchdog timer frequency can be selected from  $fs/2^{16}$ ,  $fs/2^{18}$ ,  $fs/2^{20}$

- Buzzer output, Inverted buzzer output:

Output frequency can be selected from fosc/2<sup>9</sup>, fosc/2<sup>10</sup>, fosc/2<sup>11</sup>, fosc/2<sup>13</sup>, fosc/2<sup>14</sup>, fx/2<sup>3</sup>, fx/2<sup>4</sup>.

- Remote control carrier output:

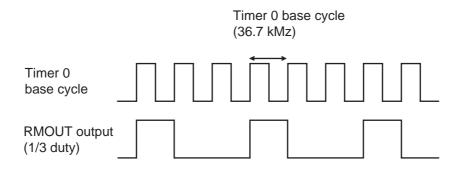

Based on the timer 0 and timer 3 output, a remote control carrier with duty cycle of 1/2 or 1/3 can be output.

- Clock output: OSC oscillation source or system clock output can be selected.

Clock source: 1/1, 1/2, 1/4, 1/16 of any one of fosc, fx, or external clock

#### - Serial interface: 4 types

Serial interface 0, 1: 2 channels

CH0: Duplex UART / Synchronous serial interface

- Transfer clock: focs/2, focs/4, focs/16, focs/64, fs/2, fs/4, 1/2 of timer 1 (timer 2) output

- Timer 1 (or timer2) is used as baud rate timer at UART.

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- It can be used as parity check, overrun error, framing error detection, or 2 channels serial interface.

CH1: Duplex UART / Synchronous serial interface

- Transfer clock: focs/2, focs/4, focs/16, focs/64, fs/2, fs/4, 1/2 of timer 1 (timer 2) output

- Timer 1 (or timer2) is used as baud rate timer at UART.

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

- It can be used as parity check, overrun error, framing error detection, or 2 channels serial interface.

- Serial interface 1 I/O (SBO1, SBI1, SBT1) can be switched to P15 to P17 or PA5 to PA7. (48 pin version only)

- Serial interface 0 I/O (SBO0, SBI0, SBT0) can be switched to P75 to P77 or PA0 to PA2. (44 pin version/ 48 version)

#### Serial interface 3: 1 channel

Single master IIC / Synchronous serial interface

- Single master handling IIC communication enable (with ACK, 9 bits are transferred)

- Transfer clock: focs/2, focs/4, focs/16, focs/32, focs/64, fs/2, fs/4, timer 2 (timer 3) output

- MSB/LSB can be selected as the first bit to be transferred. An arbitrate transfer size from 1 to 8 bits can be selected.

#### Serial interface 4: 1 channel

IIC slave interface

- IIC high-speed transfer mode (communication speed: 400 kbps)

- 7-bit or 10-bit of slave address can be set.

- General call communication mode handling

(SCL pin, SDA pin can be switched to P10, P11, or P76, P77)

- LED driver:

4 pins

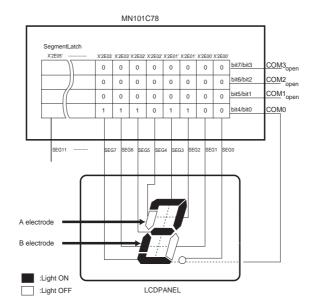

LCD driver pins:

Segment output 12 pins max. (SEG0 to SEG11)

SEG0 to SEG11 are switchable to I/O ports in unit of 1 pin.

[Note: At reset, SEG0 to SEG11 are input pors.]

Common output pins: 4 pins

COM0 to COM3 are switchable to I/O port in 1 pin unit.

Display mode selection

Static

1/2 duty, 1/2 bias

1/3 duty, 1/3 bias

1/4 duty, 1/4 bias

LCD driver clock

The source clock is the main clock (fosc):

$$1/2^{18}$$

,  $1/2^{17}$ ,  $1/2^{16}$ ,  $1/2^{15}$ ,  $1/2^{14}$ ,  $1/2^{13}$ ,  $1/2^{12}$ ,  $1/2^{11}$

The source clock is the sub-clock (fx)

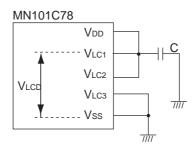

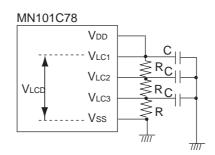

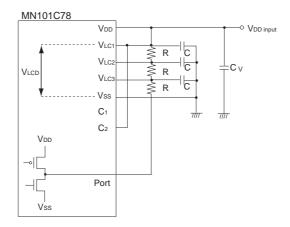

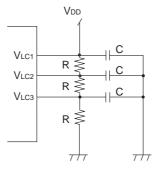

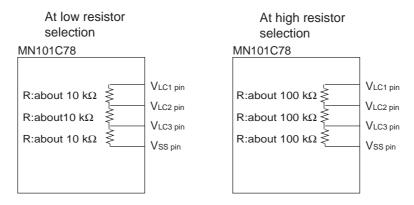

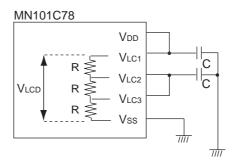

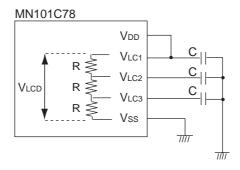

LCD power supply

Available at VDD>VLC1

External supply voltage is supplied by VLC1, VLC2, VLC3 pins or voltage applied to VLC1 is divided by internal resistance and supplied to VLC2 and VLC3 pins

| - Port: |                                                           | 48 pin          | 44 pin          |

|---------|-----------------------------------------------------------|-----------------|-----------------|

|         |                                                           | version         | version         |

|         | I/O ports                                                 | 39 pins         | 35 pins         |

|         |                                                           | (dual function) | (dual function) |

|         | LED (large current) driver pin                            | 4 pins          | 44 pins         |

|         | (switchable to timer output)                              |                 |                 |

|         | LCD power supply pin                                      | 3 pins          | 3 pins          |

|         | A/D input pin                                             | 1 pin           | 1 pin           |

|         | A/D input/ Serial interface pin                           | 6 pins          | 3 pins          |

|         | Timer I/O / LCD driver/ Remote control carrier output pin | 1 pin           | 1 pin           |

|         | Timer output/ LCD driver/ Serial interface pin            | 2 pins          | 2 pins          |

|         | Timer I/O /LCD driver/ Serial interface pin               | 1 pin           | 1 pin           |

|         | Timer I/O /Buzzer output/ LCD driver pin                  | 1 pin           | 1 pin           |

|         | Timer I/O /inverted buzzer output/ LCD driver pin         | 1 pin           | 1 pin           |

|         | IIC slave pin                                             | 2 pins          | 2 pins          |

|         | Key input/ LCD driver pin                                 | 3               | 3               |

|         | Key input/ LCD driver/ PWM output pin                     | 2               | 2               |

|         | Key input/ LCD driver/ Serial interface pin               | 1               | 1               |

|         | Key input/ LCD driver/ Serial interface/ IIC slave pin    | 2               | 2               |

|         | Common output pin                                         | 1               | 1               |

|         | Common output/ Serial interface pin                       | 3               | 3               |

|         | External interrupt pin                                    | 3               | 3               |

|         | (2 pins are used as zero cross input pin)                 |                 |                 |

|         | I/O ports                                                 | 1               | -               |

|         | XI pin                                                    | 1               | 1               |

|         | Special pin                                               | 10              | 10              |

|         | Analog reference voltage input pin                        | 1               | 1               |

|         | Operation mode input pin                                  | 1               | 1               |

|         | Reset input pin                                           | 1               | 1               |

|         | Oscillation pin (1 pin is used as I/O pin)                | 4               | 4               |

|         | Power supply pin                                          | 3               | 3               |

|         |                                                           |                 |                 |

### - Pin switching:

| <u>Serial</u> | interface I | /O |

|---------------|-------------|----|

|               |             |    |

|                         | Option 1                   | Option 2                 | Option 3            |

|-------------------------|----------------------------|--------------------------|---------------------|

| Serial interface 0      | SBT0A                      | SBT0B                    | -                   |

| Synchronous/ UART       | SBO0A/TXD0A                | SBO0B/TXD0B              |                     |

| Cynonionous/ CART       | STI0A/RXD0A                | STI0B/RXD0B              |                     |

|                         | STIONINADON                | *UART for onboard serial |                     |

|                         |                            |                          |                     |

|                         |                            | programming              |                     |

| Serial interface 1      | SBT1A                      | SBT1B                    | -                   |

| Synchronous/ UART       | SBO1A/TXD1A                | SBO1B/TXD1B              |                     |

|                         | STI1A/RXD1A                | STI1B/RXD1B              |                     |

|                         |                            | *44 pin version is not   |                     |

|                         |                            | available                |                     |

| Serial interface 3      | SBT3                       | -                        | -                   |

| Synchronous/ IIC single | SBT03                      |                          |                     |

| master                  | SBI3                       |                          |                     |

| Serial interface 4      | SDA4A                      | SDA4B                    | -                   |

| IIC slave               | SCL4A                      | SCL4B                    |                     |

|                         | *D-Wire for onboard serial |                          |                     |

|                         | programming                |                          |                     |

| Timer I/O               |                            |                          |                     |

|                         | Option 1 (I/O)             | Option 2 (output 1)      | Option 3 (output 2) |

| Timer 0                 | TM0IO                      | TM0OA                    | TM0OB               |

| Timer 1                 | TM1IO                      | -                        | -                   |

| Timer 2                 | TM2IO                      | TM2OA                    | TM2OB               |

| Timer 3                 | TM3IO                      | -                        | -                   |

| Timer 7                 | TM7IO                      | TM7O                     | -                   |

| Timer 8                 | TM8IO                      | TM8O                     | -                   |

|                         |                            |                          |                     |

# 1.3 Pin Description

### 1.3.1 Pin configuration

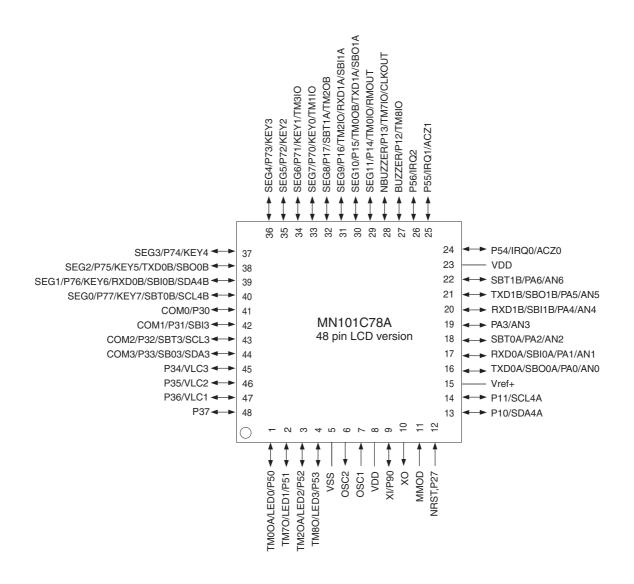

Figure:1.3.1 Pin Configuration (48TQFP: TOP VIEW)

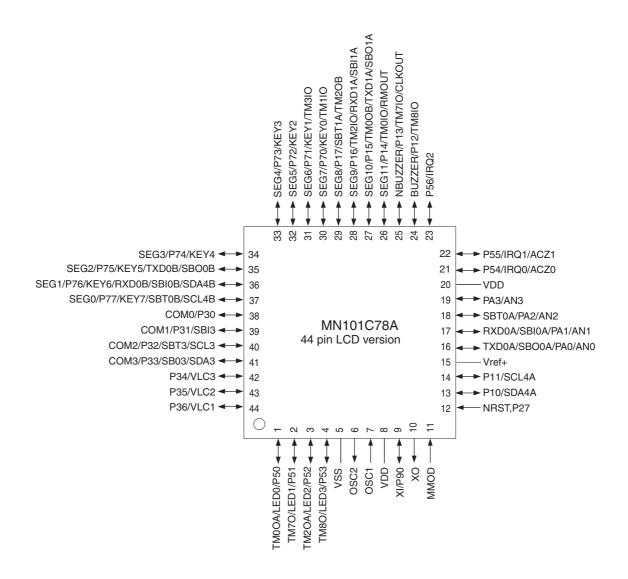

Figure:1.3.2 Pin Configuration (44QFP: TOP VIEW)

## 1.3.2 Pin Specification

Table:1.3.1 Pin Specification

| Pins   | Special F  | unctions | I/O    | Direction<br>Control | Pin<br>Control | Functions Description                 |                                                   |

|--------|------------|----------|--------|----------------------|----------------|---------------------------------------|---------------------------------------------------|

| P10    | SDA4A      |          | in/out | P1DIR0               | P1PLU0         | SDA4A: IIC4 Data I/O                  |                                                   |

| P11    | SCL4A      |          | in/out | P1DIR1               | P1PLU1         | SCL4A: IIC4 Clock I/O                 |                                                   |

| P12    | TM8IO      | BUZZER   | in/out | P1DIR2               | P1PLU2         | TM8IO: Timer 8 I/O                    | BUZZER: Buzzer output                             |

| P13    | TM7IO      | NBUZZER  | in/out | P1DIR3               | P1PLU3         | TM7IO: Timer 7 I/O                    | NBUZZER: Buzzer reverse output                    |

|        | CLKOU<br>T |          |        |                      |                | CLKOUT: Frequency output              |                                                   |

| P14    | TM0IO      | RMOUT    | in/out | P1DIR4               | P1PLU4         | TM0IO: Timer 0 I/O                    | RMOUT: Remote control carrier output              |

|        | SEG11      |          |        |                      |                | SEG11: Segment output                 |                                                   |

| P15    | ТМ00В      | SB01A    | in/out | P1DIR5               | P1PLU5         | TMOOB: Timer 8 I/O                    | SB01A: Serial interface transmission data output  |

|        | TXD1A      | SEG10    |        |                      |                | TXD1A: UART1 transmission data output | SEG10: Segment output                             |

| P16    | TM2IO      | SBI1A    | in/out | P1DIR6               | P1PLU6         | TM2IO: Timer 2 I/O                    | SBI1A: Serial interface 1 reception data input    |

|        | RXD1A      | SEG9     | in/out |                      |                | RXD1A: UART1 reception data input     | SEG9: Segment output                              |

| P17    | TM2OB      | SBT1A    | in/out | P1DIR7               | P1PLU7         | TM2OB: Timer 2 output                 | SBT1A: Serial interface 1 clock I/O               |

|        | SEG8       |          |        |                      |                | SEG8: Segment output                  |                                                   |

| P27    | NRST       |          | in     | -                    | -              | NRST: Reset                           |                                                   |

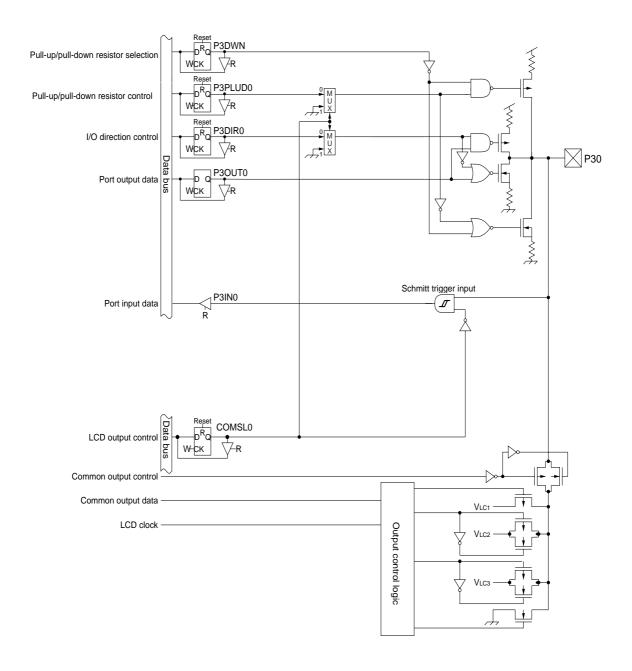

| P30    | COM0       |          | in/out | P3DIR0               | P3PLU0         | COM0: LCD common output               |                                                   |

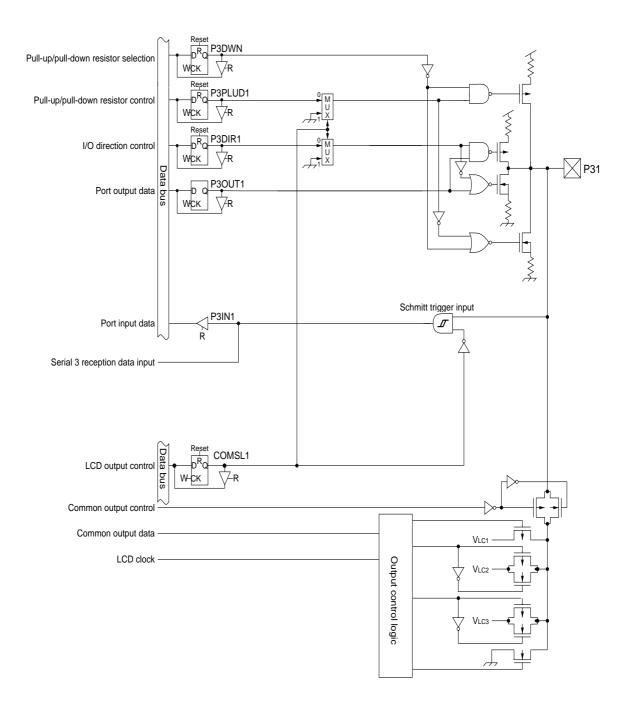

| P31    | SBI3       | COM1     | in/out | P3DIR1               | P3PLU1         | COM1: LCD common output               | SBI3: Serial interface 3 reception data input     |

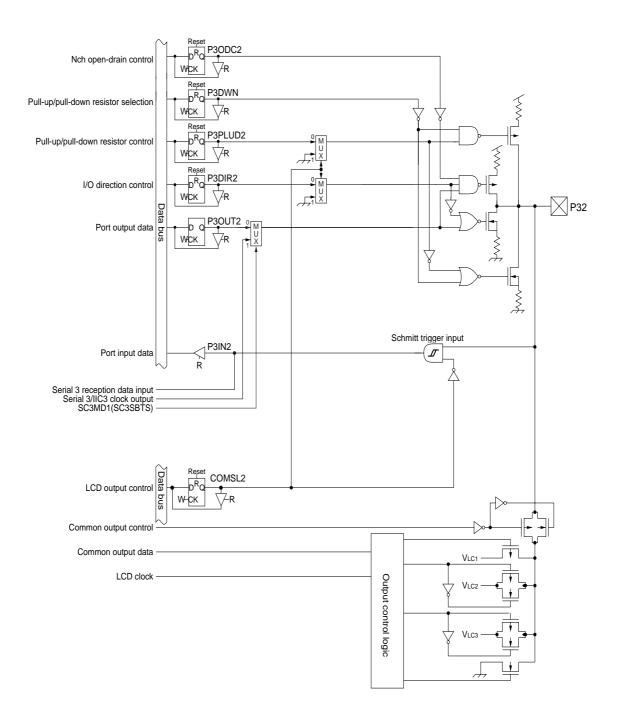

| P32    | SBT3       | SCL3     | in/out | P3DIR2               | P3PLU2         | COM2: LCD common output               | SBT3: Serial interface 3 clock I/O                |

|        | COM2       |          |        |                      |                | SCL3: IIC3 clock output               |                                                   |

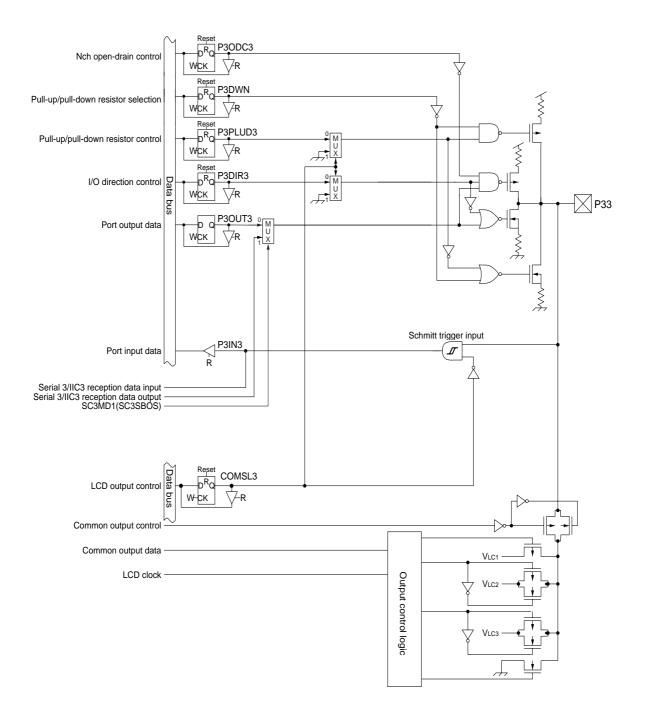

| P33    | SBO3       | SDA3     | in/out | P3DIR3               | P3PLU3         | COM3: LCD common output               | SBO3: Serial interface 3 transmission data output |

|        | СОМЗ       |          |        |                      |                | SDA3: Serial data I/O                 |                                                   |

| P34    | VLC3       |          | in/out |                      |                | VLC3: LCD power                       |                                                   |

| P35    | VLC2       |          | in/out |                      |                | VLC2: LCD power                       |                                                   |

| P36    | VLC1       |          | in/out | -                    | -              | VLC1: LCD power                       |                                                   |

| P37 *1 |            |          | in/out | P3DIR7               | P3PLU7         |                                       |                                                   |

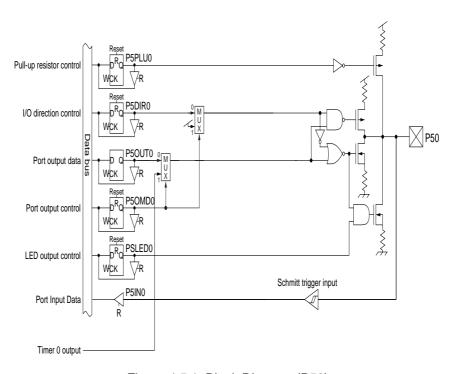

| P50    | TM0OA      | LED0     | in/out | P5DIR0               | P5PLU0         | TM0OA: Timer 0 output                 | LED0: LED driver pin 0                            |

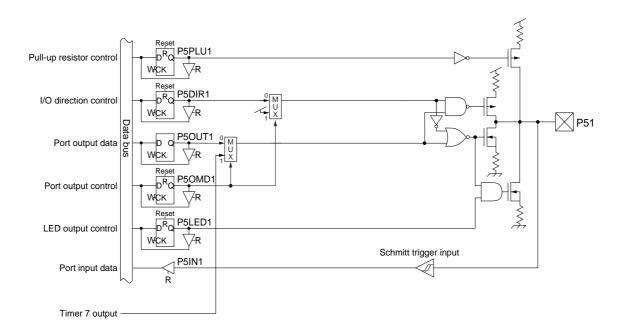

| P51    | TM7O       | LED1     | in/out | P5DIR1               | P5PLU1         | TM70: Timer 7 output                  | LED1: LED driver pin 1                            |

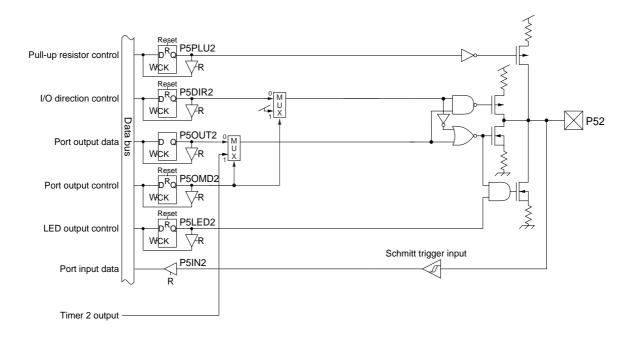

| P52    | TM2OA      | LED2t    | in/out | P5DIR2               | P5PLU2         | TM2OA: Timer 2 output                 | LED2: LED driver pin 2                            |

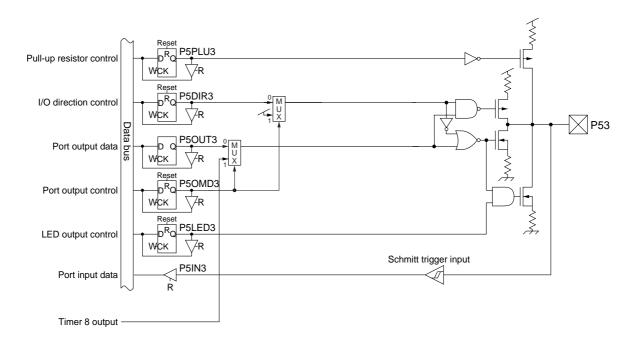

| P53    | TM8O       | LED3     | in/out | P5DIR3               | P5PLU3         | TM8O: Timer 8 output                  | LED3: LED driver pin 3                            |

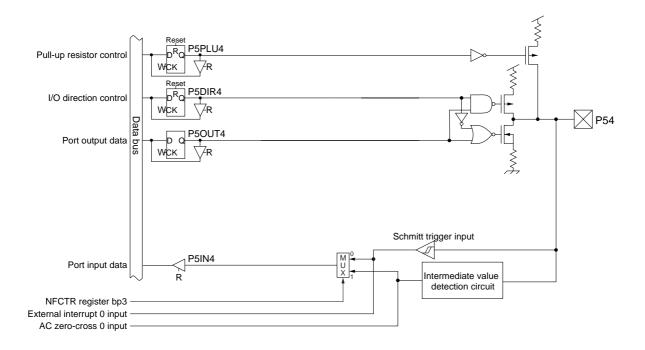

| P54    | IRQ0       | ACZ0     | in/out | P5DIR4               | P5PLU4         | IRQ0: External interrupt 0            | ACZ0: Zero cross input 0                          |

| P55    | IRQ1       | ACZ1     | in/out | P5DIR5               | P5PLU5         | IRQ1: External interrupt 1            | ACZ1: Zero cross input 1                          |

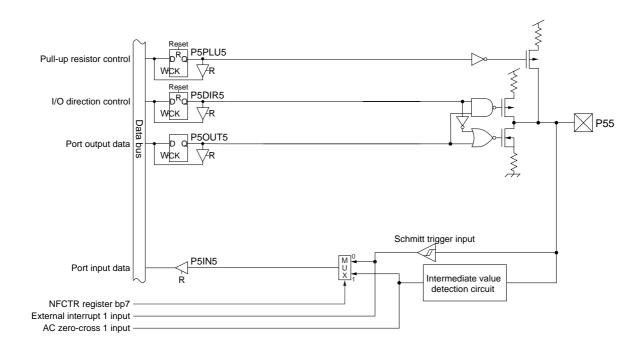

| P56    | IRQ2       |          | in/out | P5DIR6               | P5PLU6         | IRQ2: External interrupt 2            |                                                   |

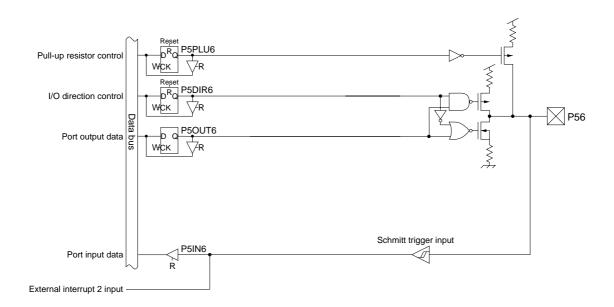

| P70    | TM1IO      | KEY0     | in/out | P7DIR0               | P7PLU0         | TM1IO: Timer 1 I/O                    | KEYO: Key interrupt input 0                       |

|        | SEG7       |          |        |                      |                | SEG7: Segment output                  |                                                   |

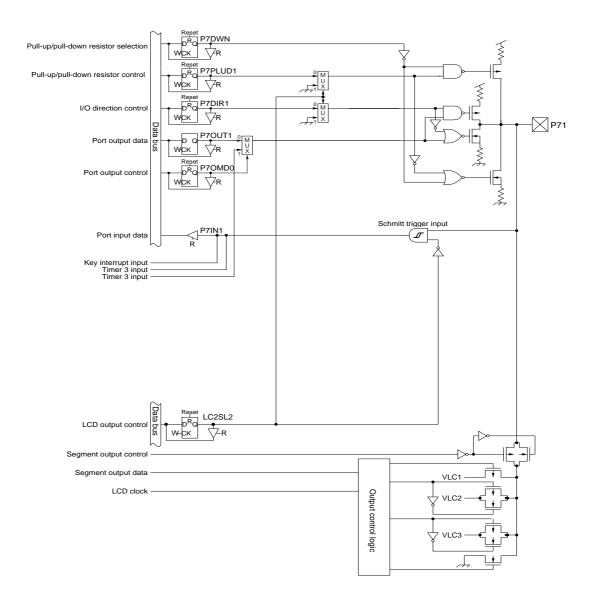

| P71    | TM3IO      | KEY1     | in/out | P7DIR1               | P7PLU1         | TM3IO: Timer 1 I/O                    | KEY1: Key interrupt input 1                       |

|        | SEG6       |          |        |                      |                | SEG6: Segment output                  |                                                   |

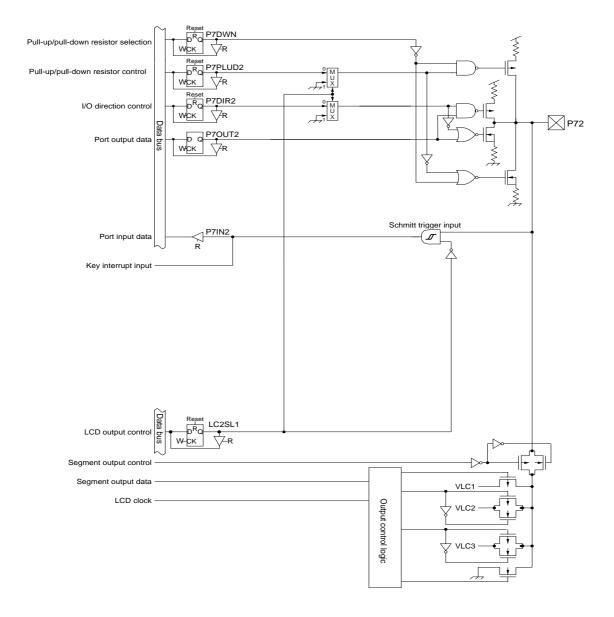

| P72    | KEY2       | SEG5     | in/out | P7DIR2               | P7PLU2         | KEY2: Key interrupt input 2           | SEG5: Segment output                              |

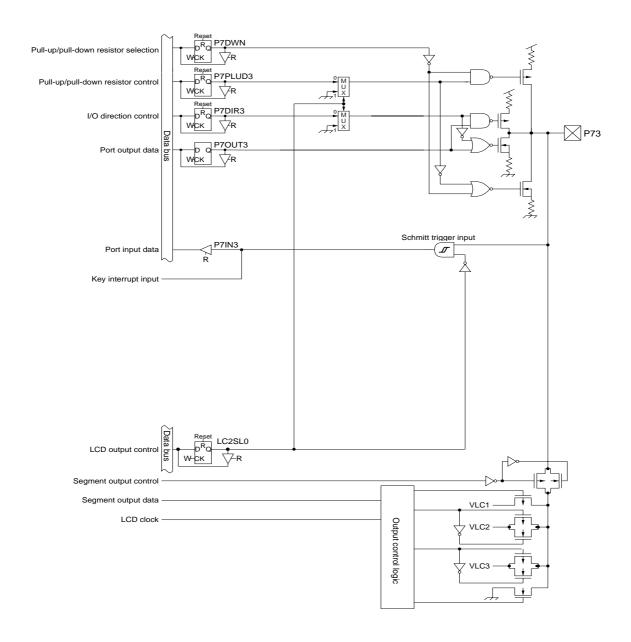

| P73    | KEY3       | SEG4     | in/out | P7DIR3               | P7PLU3         | KEY3: Key interrupt input 3           | SEG4: Segment output                              |

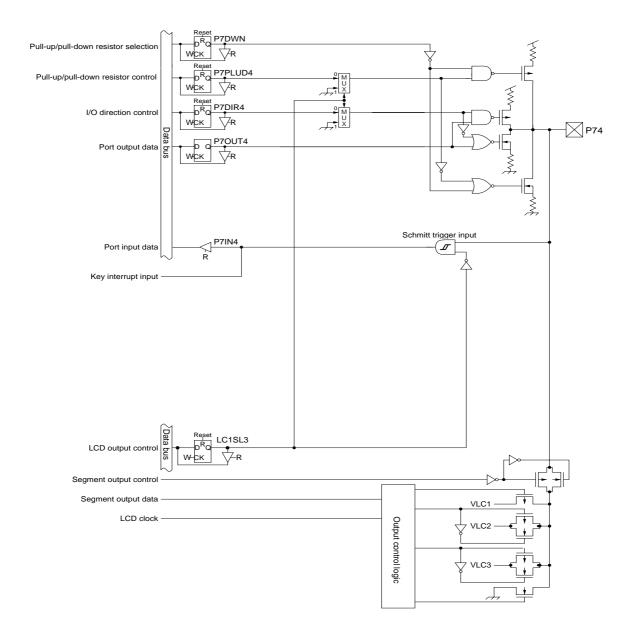

| P74    | KEY4       | SEG3     | in/out | P7DIR4               | P7PLU4         | KEY4: Key interrupt input 4           | SEG3: Segment output                              |

| Pins      | Special F | unctions | I/O    | Direction<br>Control | Pin<br>Control | Functions Description                              |                                       |

|-----------|-----------|----------|--------|----------------------|----------------|----------------------------------------------------|---------------------------------------|

| P75       | SBO0B     | TXD0B    | in/out | P7DIR5               | P7PLU5         | SBO0B: Serial interface 0 transmission data output | TXD0B: UART0 transmission data output |

|           | KEY5      | SEG2     |        |                      |                | KEY5: Key interrupt input 5                        | SEG2: Segment output                  |

| P76       | SBIOB     | RXDOB    | in/out | P7DIR6               | P7PLU6         | SBI0B: Serial interface 0 reception data input     | RXD0B: UART0 reception data input     |

|           | SDA4B     | KEY6     |        |                      |                | SDA4B:IIC4 data I/O                                | KEY6: KEY interrupt input 6           |

|           | SEG1      |          |        |                      |                | SEG1: Segment output                               |                                       |

| P77       | SBT0B     | SCL4B    | in/out | P7DIR7               | P7PLU7         | SBT0B: Serial interface 0 clock I/O                | SCL4B: IIC4 clock I/O                 |

|           | KEY7      | SEG0     |        |                      |                | KEY7: Key interrupt input 7                        | SEG0: Segment 0 output                |

| P90       | XI        |          | in     | P9DIR0               | P9PLU0         | XI: Low speed frequency input pin                  |                                       |

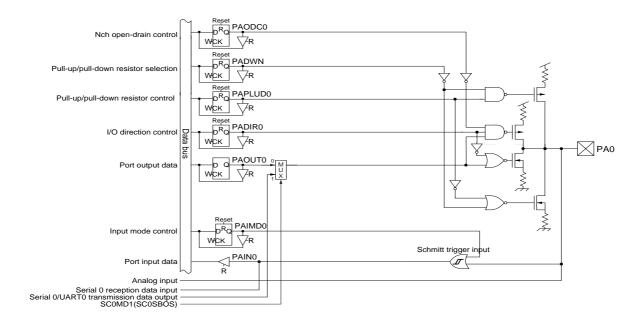

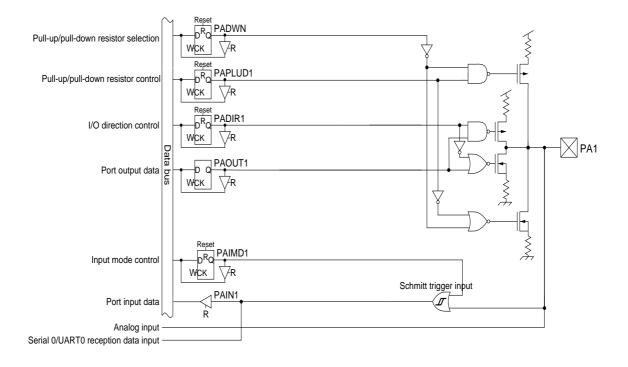

| PA0       | SBO0A     | TXD0A    | in/out | PADIR0               | PAPLU0         | SBO0A: Serial interface 0 data output              | TXD0A: UART0 transmission data output |

|           | AN0       |          |        |                      |                | AN0: Analog 0 input                                |                                       |

| PA1       | SBI0A     | RXD0A    | in/out | PADIR1               | PAPLU1         | SBI0A: Serial interface 0 data input               | RXD0A: UART0 reception data input     |

|           | AN1       |          |        |                      |                | AN1: Analog 1 input                                |                                       |

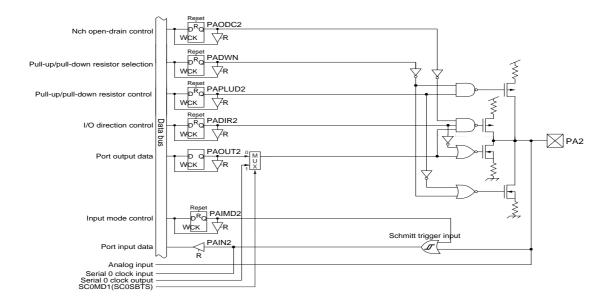

| PA2       | SBT0A     | AN2      | in/out | PADIR2               | PAPLU2         | SBT0A: Serial interface 0 clock I/O                | AN2: Analog 2 input                   |

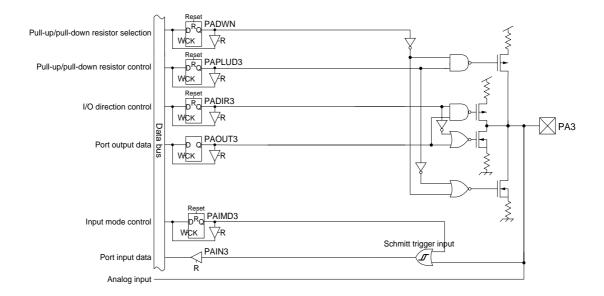

| PA3       | AN3       |          | in/out | PADIR3               | PAPLU3         | AN3: Analog 3 input                                |                                       |

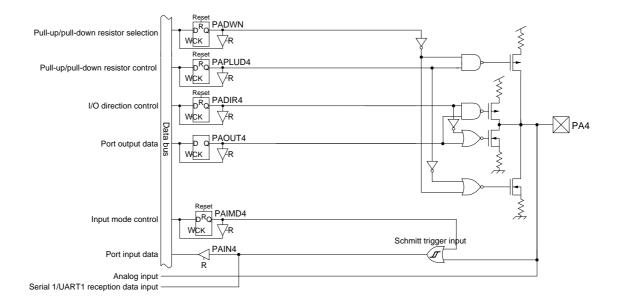

| PA4<br>*1 | AN4       |          | in/out | PADIR4               | PAPLU4         | AN4: Analog 4 input                                |                                       |

|           | SBI1B     | RXD1B    |        |                      |                | SBI1B: Serial interface 1 data input               | RXD1B: UART1 reception data input     |

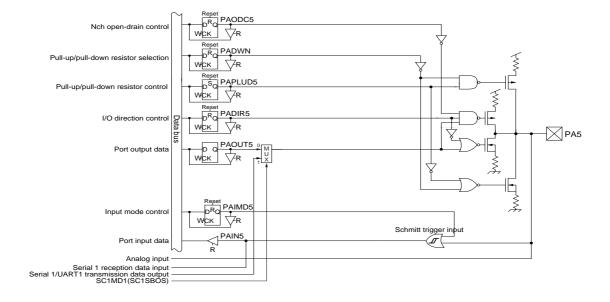

| PA5<br>*1 | SBO1B     | TXD1B    | in/out | PADIR5               | PAPLU5         | SBO1B: Serial interface 1 transmission data output | TXD1B: UART1 transmission data output |

|           | AN5       |          |        |                      |                | AN5: Analog 5 input                                |                                       |

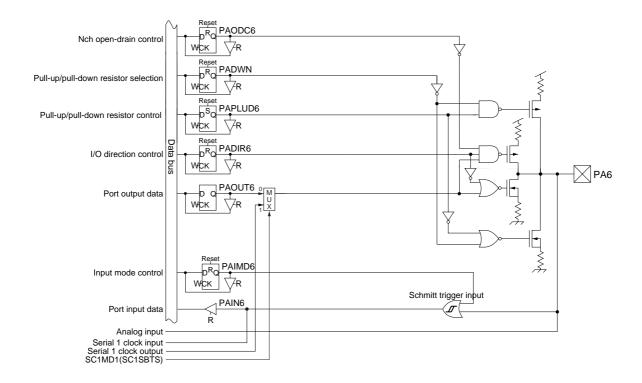

| PA6<br>*1 | SBT1B     | AN6      | in/out | PADIR6               | PAPLU6         | SBT1B: Serial interface 1 clock I/O                | AN6: Analog 6 input                   |

<sup>\* 1</sup> Not available for 44 pin QFP package

### 1.3.3 Pin Functions

Table:1.3.2 Pin Functions

| Name                                                 | TQFP 48<br>Pin No.                           | QFP44<br>Pin No.                             | I/O             | Other Function                                                                                                                                                       | Function                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub><br>V <sub>DD</sub><br>Vref +         | 5<br>8, 23<br>15                             | 5<br>8, 20<br>15                             | -               |                                                                                                                                                                      | Power supply pins                     | Supply 1.8 V to 3.6 V to $V_{DD}$ and 0 V to $V_{SS}$ . For MN101CF78A, supply 2.7 V to 3.6 V to $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

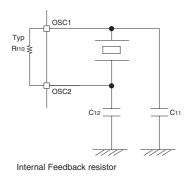

| OSC1<br>OSC2                                         | 7<br>6                                       | 7<br>6                                       | Input<br>Output |                                                                                                                                                                      | Clock input pins<br>Clock output pins | Connect these oscillation pins to ceramic or crystal oscillators for high-frequency clock operation.  If the clock is an external input, connect it to OSC1 and leave OSC2 open. The chip will not operate with an external clock when using either the STOP or SLOW modes.                                                                                                                                                                                                                                                                                                                                                                                           |

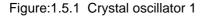

| XI<br>XO                                             | 9 10                                         | 9 10                                         | Input<br>Output | P90                                                                                                                                                                  | Clock input pins<br>Clock output pins | Connect these oscillation pins to crystal oscillators for low-frequency clock operation. If the clock is an external input, connect it to XI and leave XO open. When using the STOP mode, the chip will not operate with an external clock. If these pins are not used, connect XI to V <sub>SS</sub> and leave XO open.                                                                                                                                                                                                                                                                                                                                              |

| NRST                                                 | 12                                           | 12                                           | Input           | P27                                                                                                                                                                  | Reset pins<br>[Active low]            | This pin resets the chip when power is turned on, is allocated as P27 and contains an internal pull-up resistor (Type. 35 kw). Setting this pin "L" level initialize the internal state of the device. Thereafter, setting the input to "H" level releases the reset. The hardware waits for the system clock to stabilize, then processes the reset interrupt. Also, if "0" is written to P27 and the reset is initiated by software, "L" level will be output. The output has an N-ch open-drain configuration. If a capacitor is to be inserted between NRST and $\rm V_{SS}$ , it is recommended that a discharge diode be placed between NRST and $\rm V_{DD}$ . |

| P10<br>P11<br>P12<br>P13<br>P14<br>P15<br>P16<br>P17 | 13<br>14<br>27<br>28<br>29<br>30<br>31<br>32 | 13<br>14<br>24<br>25<br>26<br>27<br>28<br>29 | I/O             | SDA4A<br>SCL4A<br>TM8IO, BUZZER<br>TM7IO, NBUZZER, CLKOUT<br>TM0IO, RMOUT, SEG11<br>TM0OB, SBO1A, TXD1A,<br>SEG10<br>TM2IO, SBI1A, RXD1A, SEG9<br>TM2OB, SBI1A, SEG8 | I/O port 0                            | 8-bit COMS tri-state I/O port. Each bit can be set individually as either an input or output by the P1DIR register. A pull-up / pull-down resistor for each bit can be selected individually by the P1PLU register. A pull-up / pull-down resistor for each port can be selected individually by the SELUD register. (However, pull-up and pull-down resistors cannot be mixed.) At reset, the input mode is selected and P10, P11 are pull-up resistor enable ("H" output), P12 to P17 are pull-up resistor disable (output"H", "Hi-Z").                                                                                                                             |

| MMOD                                                 | 11                                           | 11                                           | Input           |                                                                                                                                                                      | Memory mode setting pins              | Input always "L" level. It is used for Flash programming only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P27                                                  | 12                                           | 12                                           | Input           | NRST                                                                                                                                                                 | I/O port 2                            | Port P27 has an N-ch open-drain configuration. When "0" is written and the reset is initiated by software, "L" level will be output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                         | TOED 40                                      | OED44                                        | 1   |                                                                                                                                                                                |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------|----------------------------------------------|----------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                    | TQFP 48<br>Pin No.                           | QFP44<br>Pin No.                             | I/O | Other Function                                                                                                                                                                 | Function                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

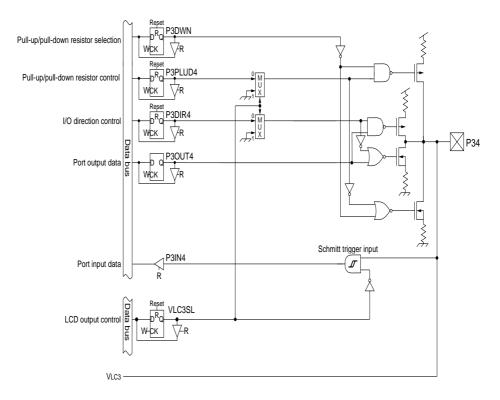

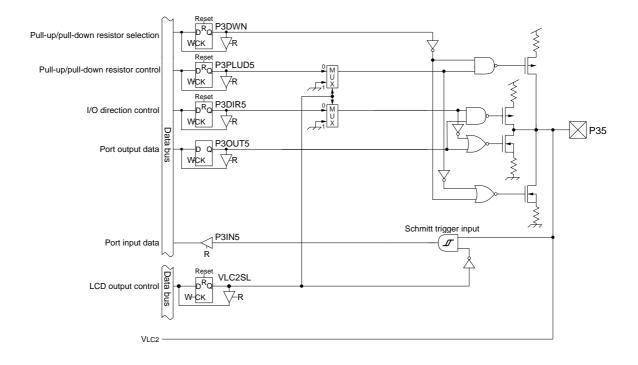

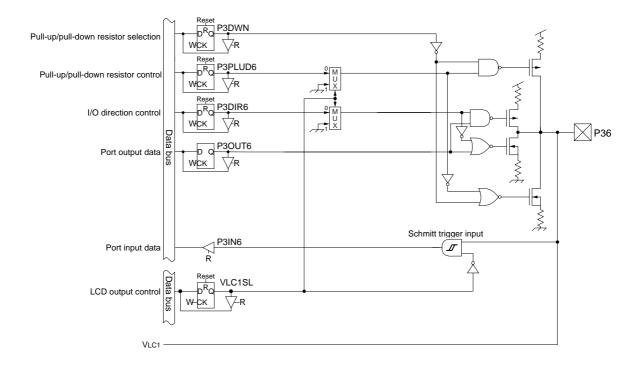

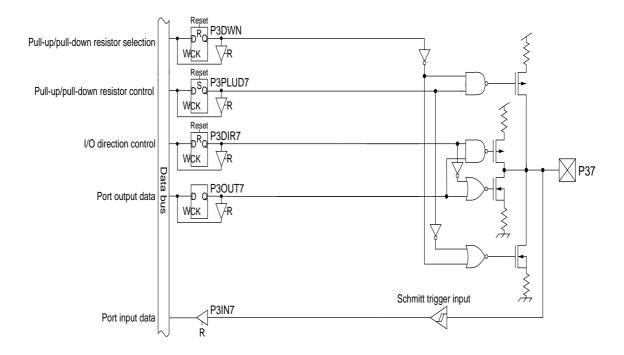

| P30<br>P31<br>P32<br>P33<br>P34<br>P35<br>P36<br>P37 *1 | 41<br>42<br>43<br>44<br>45<br>46<br>47<br>48 | 38<br>39<br>40<br>41<br>42<br>43<br>44       |     | COM0<br>SBI3, COM1<br>SBT3, SCL3, COM2<br>SBO3, SDA3, COM3<br>VLC3<br>VLC2<br>VLC1                                                                                             | I/O port 3                                           | 8-bit COMS tri-state I/O port. Each bit can be set individually as either an input or output by the P3DIR register. A pull-up resistor for each bit can be selected individually by the P3PLU register. At reset, the input mode is selected and P37is pull-up resistor enable ("H" output), P31 to P37 are pull-up resistor disable (output "H", "Hi-Z").                                                                                                                                                                                                                                            |

| P50<br>P51<br>P52<br>P53<br>P54<br>P55<br>P56           | 1<br>2<br>3<br>4<br>24<br>25<br>26           | 1<br>2<br>3<br>4<br>21<br>22<br>23           | I/O | TM0OA, LED0<br>TM7O, LED1<br>TM2OA, LED2<br>TM8O, LED3<br>IRQ0, ACZ0<br>IRQ1, ACZ1<br>IRQ2                                                                                     | I/O port 5                                           | 7-bit COMS tri-state I/O port. Each bit can be set individually as either an input or output by the P5DIR register. A pull-up resistor for each bit can be selected individually by the P5PLU register. Also, at output, LED direct drive is enabled for P50 to P53. At reset, the input mode is selected and pull-up resistors are disabled (output "H", "Hi-Z").                                                                                                                                                                                                                                    |

| P70<br>P71<br>P72<br>P73<br>P74<br>P75<br>P76           | 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40 | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | I/O | TM1IO, KEY0, SEG7<br>TM3IO, KEY1, SEG6<br>KEY2, SEG5<br>KEY3, SEG4<br>KEY4, SEG3<br>SBO0B, TXD0B, KEY5, SEG2<br>SBI0B, RXD0B, SDA4B,<br>KEY6, SEG1<br>SBT0B, SCL4B, KEY7, SEG0 | I/O port 7                                           | 8-bit COMS tri-state I/O port. Each bit can be set individually as either an input or output by the P7DIR register. A pull-up / pull-down resistor for each bit can be selected individually by the P7PLU register. A pull-up / pull-down resistor for each port can be selected individually by the SELUD register. (However, pull-up and pull-down resistors cannot be mixed.) At reset, the input mode is selected and pull-up resistors are disabled (output "H", "Hi-Z").                                                                                                                        |

| P90                                                     | 9                                            | 9                                            | I/O | XI                                                                                                                                                                             | I/O port 9                                           | 8-bit COMS tri-state I/O port. Each bit can be set individually as either an input or output by the P9DIR register. A pull-up / pull-down resistor for each bit can be selected individually by the P9PLU register. Also, by XSEL register, the pin can be switched to oscillation input pin which connects to crystal oscillators for low-frequency clock operation. If the clock is an external input, connect it to XI and leave XO open. At the STOP mode, the chip will not operate with an external clock. At reset, the input mode is selected and pull-up resistors are enabled ("H" output). |

| PA0<br>PA1<br>PA2<br>PA3<br>PA4 *1<br>PA5 *1<br>PA6 *1  | 16<br>17<br>18<br>19<br>20<br>21<br>22       | 16<br>17<br>18<br>19                         | I/O | AN0, SBO0A, TXD0A<br>AN1, SBI0A, RXD0A<br>AN2, SBT0A<br>AN3<br>AN4, SBI1B, RXD1B<br>AN5, SBO1A, TXD1B<br>AN6, SBT1B                                                            | I/O port A                                           | 7-bit COMS tri-state I/O port. Each bit can be set individually as either an input or output by the P7DIR register. At reset, the input mode is selected and pullup resistors are disabled (high impedance output).                                                                                                                                                                                                                                                                                                                                                                                   |

| SBO0A<br>SBO0B<br>SBO1A<br>SBO1B *1<br>SBO3             | 16<br>38<br>30<br>21<br>44                   | 16<br>35<br>27<br>41                         | I/O | PA0, AN0, TXD0A<br>P75, KEY5, RXD0B, SEG2<br>P15, TXD1A, TM0OB, SEG10<br>PA5, AN5, TXD1B<br>P33, COM3                                                                          | Serial interface<br>transmission data<br>output pins | Transmission data output pins for serial interface 0, 1, 3.  The output configuration, either COMS pushpull or Nch open-drain can be selected at the P10DC, P3ODC, P7ODC, PAODC registers. Pull-up and pull-down registers can be selected by the P1PLUD, P3PLU, P7PLUD, PAPLU registers. Select the output mode at the PADIR registers and serial data output mode by serial mode register 1 (SC0MD1, SC1MD1, SC3MD1).  These can be used as normal I/O pins when the serial interface is not used.                                                                                                  |

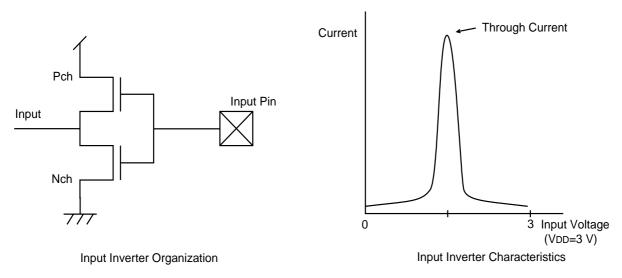

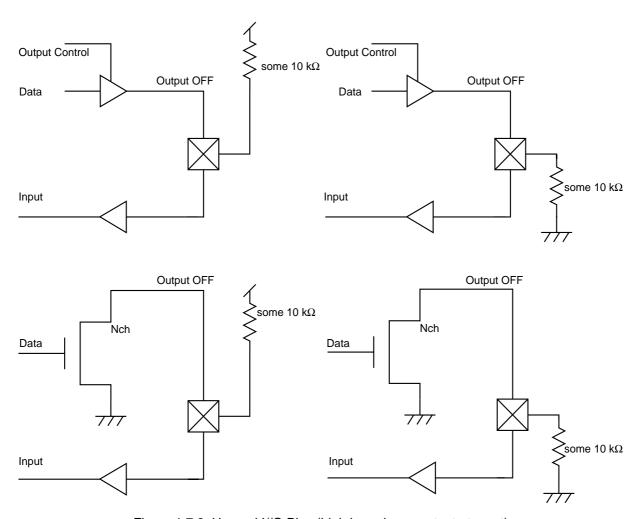

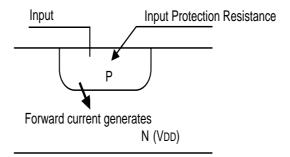

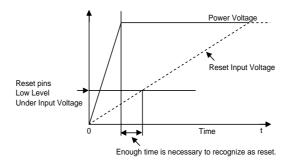

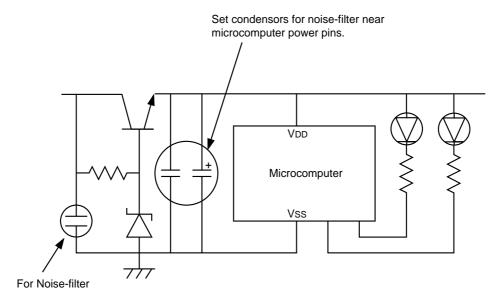

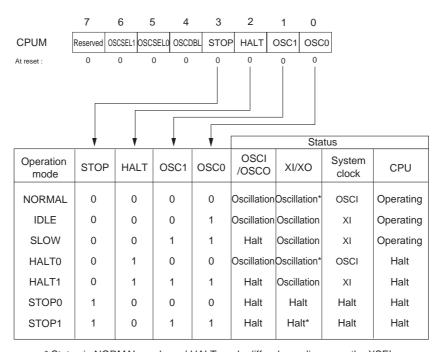

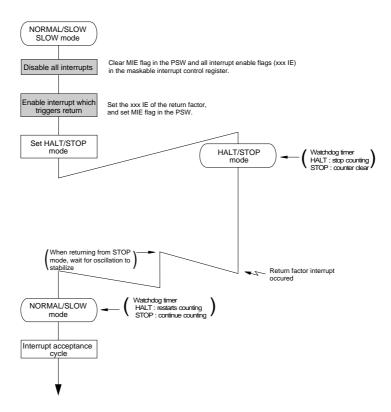

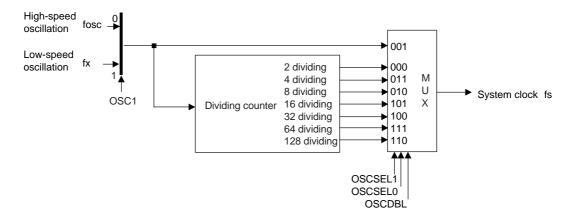

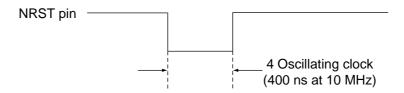

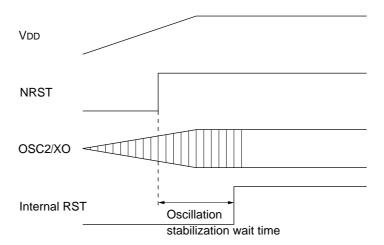

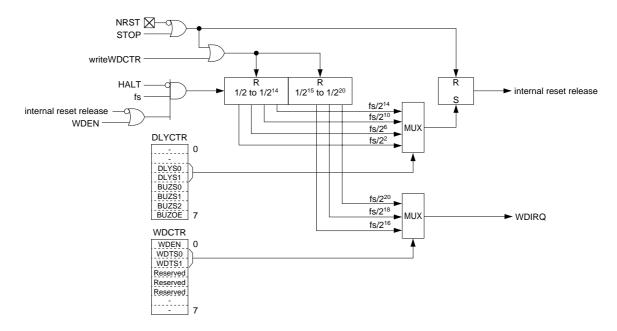

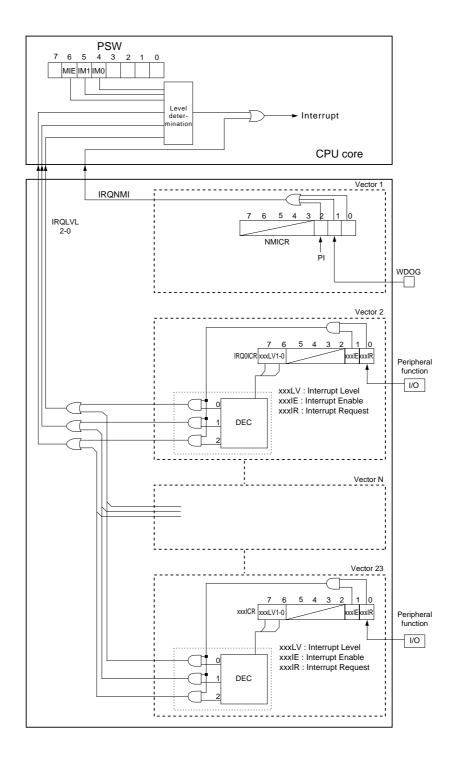

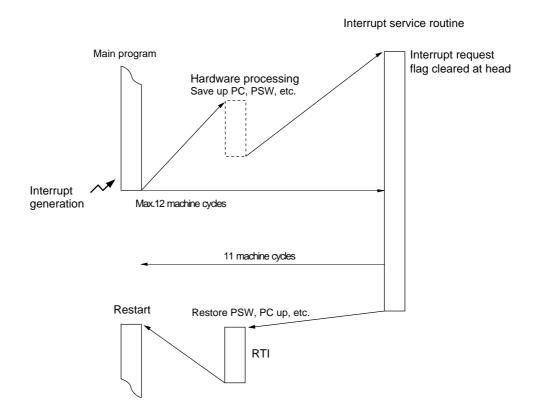

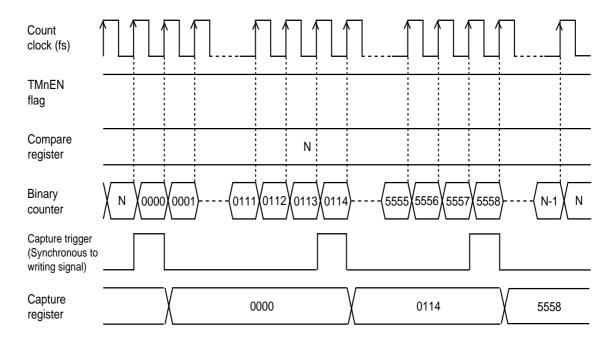

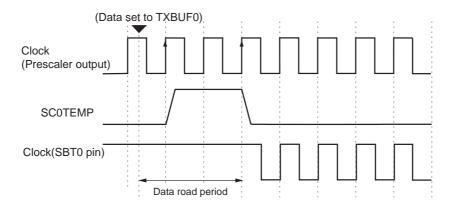

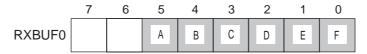

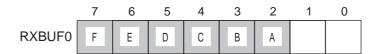

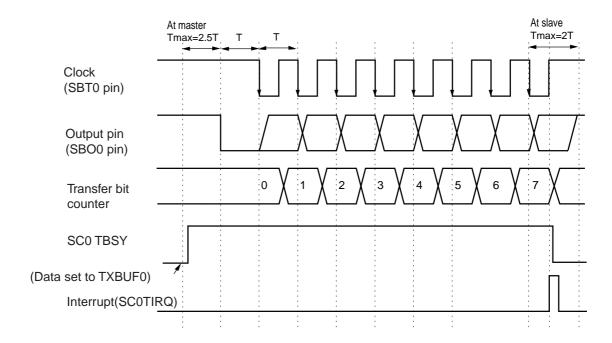

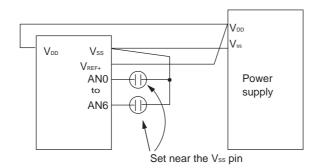

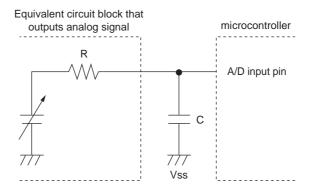

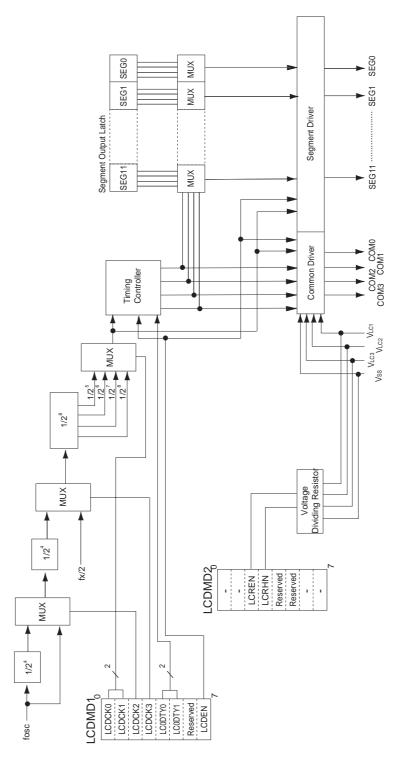

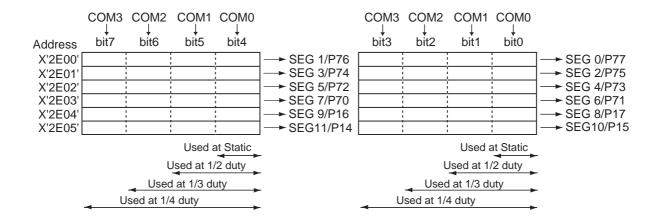

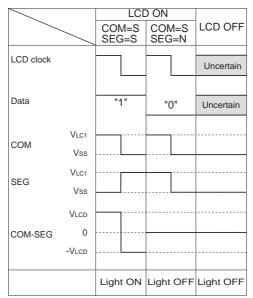

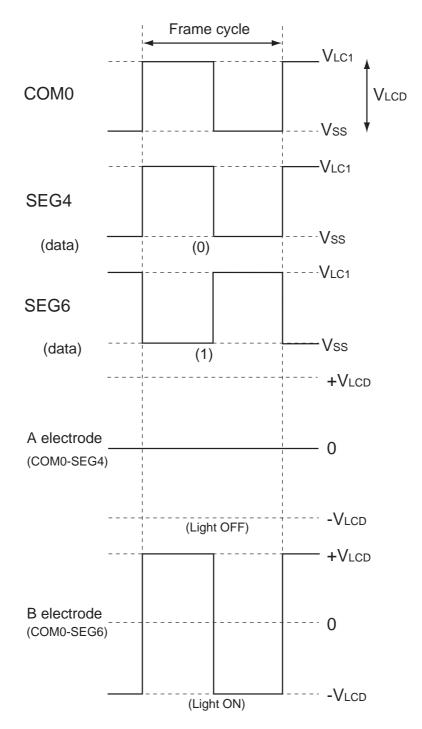

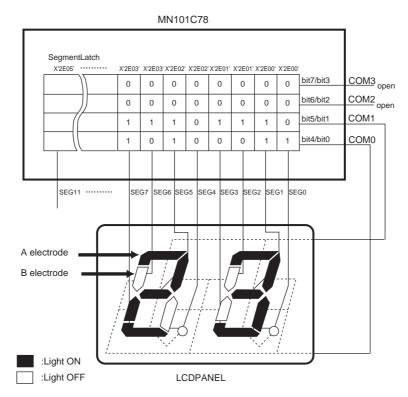

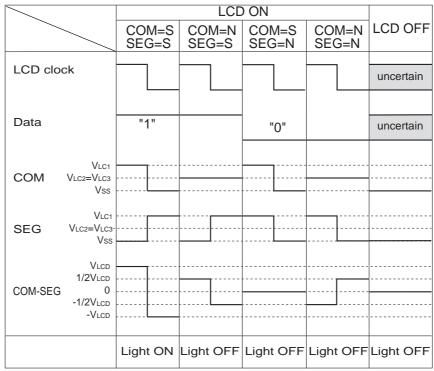

| Name                                        | TQFP 48<br>Pin No.         | QFP44<br>Pin No.     | I/O    | Other Function                                                                                       | Function                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |