Tin tức

SiLabs nhắm tới 56Gbit / giây với chip đồng hồ tốc độ thấp

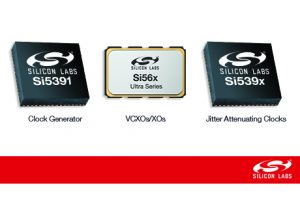

Si5391 là bộ tạo xung nhịp "bất kỳ tần số" với tối đa 12 đầu ra và bộ tách pha RMS phụ 100f.

Một phiên bản hiệu chuẩn chính xác (‘P-grade’) thường đạt được độ lệch pha 69fs RMS và có thể tạo ra các tần số chính cần thiết trong các thiết kế serdes 56Gbit / s. Công ty mô tả nó như là một 'sub-100-f-clock-tree-on-a-chip' thực sự đáp ứng yêu cầu jitter đồng hồ tham chiếu PAM-4 56G với biên độ.

Si5395 / 4/2 là bộ suy giảm jitter cho cơ sở hạ tầng Internet có thể tạo ra bất kỳ sự kết hợp của tần số đầu ra từ bất kỳ tần số đầu vào nào trong khi cung cấp jitter pha 90fs RMS. Một lần nữa, các thiết bị cấp P cung cấp 69 jMS giai đoạn jitter điển hình.

Dòng sản phẩm VCXO và XO "Ultra Series" của Si56x có thể tùy chỉnh với mọi tần số lên tới 3 GHz, hỗ trợ gấp đôi dải tần số hoạt động của các sản phẩm VCXO của Silicon Labs trước đó với một nửa số lượng jitter, theo hãng.

Chúng có các tùy chọn lập trình đơn, kép, quad và I2C trong các phiên bản 5 x 7mm và 3,2 x 5mm. Sử dụng bao bì tiêu chuẩn có nghĩa là họ sẽ thả một số ổ cắm bị chiếm đóng bởi XO, VCXO và VCSO trước đó. Jitter giai đoạn điển hình là thấp như 90fs.

Si54x Ultra Series XO dành cho các ứng dụng đòi hỏi sự ổn định chặt chẽ hơn và đảm bảo độ tin cậy lâu dài, chẳng hạn như mạng truyền dẫn quang (OTN), thiết bị băng rộng, trung tâm dữ liệu và hệ thống công nghiệp.

Chúng được thiết kế riêng cho 56Gbit / s PAM-4 (điều chế biên độ xung bốn mức) để tăng tốc độ bit trên mỗi kênh trong khi vẫn giữ được độ rộng băng thông. Jitter giai đoạn điển hình là thấp như 80 fs.